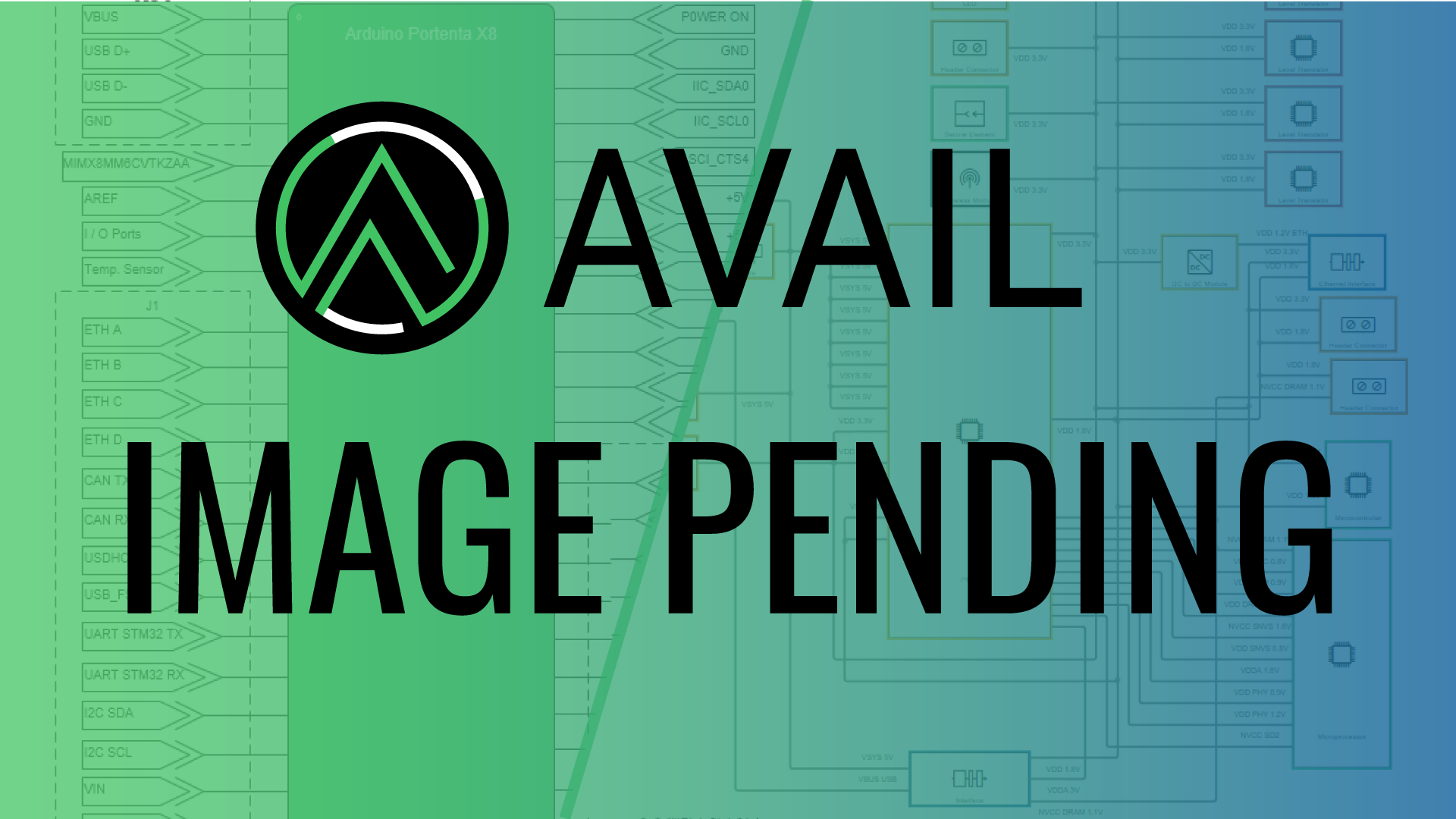

Cost-Optimized AMD Zynq UltraScale+ MPSoC ZU4/ZU5/ZU6/ZU7/ZU9 Power Tree based on NXP Solution

Grayed out parts are unavailable for purchase on Avnet Silica.

The displayed part lists is a small subset of the complete BOM.

| MFGR | PART# | BLK NM |

|---|---|---|

| NXP | MPF5200AMBA0ES | PMIC |

| NXP | MC33PF8101A0ES | PMIC |

| NXP | MFS5600AVMA0EPR2 | PMIC |

IMPORTANT NOTICE AND DISCLAIMER: AVNET PROVIDES THESE DESIGN FILES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY. SEE LEGAL NOTICES | AVNET EMEA FOR ADDITIONAL INFORMATION.