# ESSENTIALS OF EDGE COMPUTING

#### All proceeds go to IGNITE Worldwide

NXP is committed to inspiring the next generation of technologists. All proceeds from the sale of this book will go to IGNITE Worldwide, a nonprofit organization dedicated to advancing gender and racial equity in Science, Technology, Engineering, and Math (STEM).

IGNITE Worldwide provides a sustainable, scalable, and effective award-winning program that works directly with educators during the school day to reach girls, nonbinary, transgender, and agender students. The IGNITE Program, which is provided cost-free to schools, removes barriers faced by low-income and marginalized youth, providing them the possibility to envision, engage, and pursue STEM education and career opportunities.

To learn more about IGNITE Worldwide visit www.igniteworldwide.org.

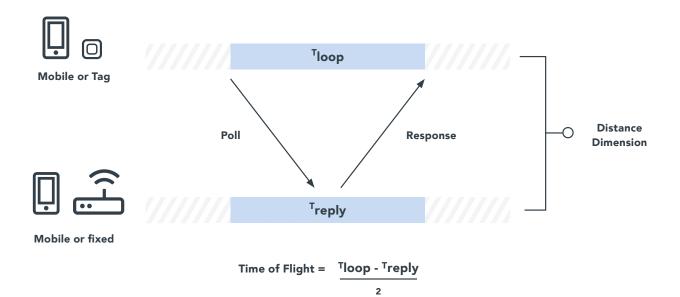

#### **FOREWORD**

We anticipate a huge leap in the smart things that make up the edge of everything in our homes, offices, factories, and vehicles. The 50 billion smart connected devices expected by 2025 can influence how individuals, communities and entire industries communicate, learn and operate. These devices will anticipate our needs and automate our environments. As an industry, it is up to all of us to ensure they meet the ultimate goals for society – a greener, safer, and more productive society. No single company can do this alone. It's a collective effort that requires expertise across an ecosystem of semiconductor suppliers, software partners and device makers.

Widespread adoption of these smart connected devices means enormous amounts of data will be created, which is why the edge is fast becoming a requirement for the next era of the IoT. The edge puts processing power where data is generated. At the heart is silicon, but the end-to-end architecture of an edge device is much more complex than the silicon itself. Deeply intertwined in the silicon is software that brings advancements in security, low power, machine learning, and connectivity.

This book was created to share knowledge and insights to help the industry unravel this complexity and drive forward the enormous potential of the edge. Whether you're creating SoCs or edge products, you are an enabler of a society that is greener, safer and more productive. I hope you find information in this book useful for your tasks towards realizing the future edge of everything.

#### **Ron Martino**

Executive Vice President and General Manager Edge Processing NXP Semiconductors

#### **PREFACE**

Computing at the edge of a network is a fundamentally simple concept, but it requires a broad range of capabilities to achieve optimal security, energy efficiency, connectivity and machine learning intelligence. In *Essentials of Edge Computing*, you'll find insights and best practices on a wide range of these emerging edge computing design concepts that you can apply in your next application.

I would like to thank many key contributors who have made this book possible, including Mohit Arora, Jean-Christophe Bodet, Antoine Boiteau, Cristi Caciuloiu, Brian Carlson, Nicolas Collonvillé, Julien Delplancke, Silvano di Ninno, Alexandra Dopplinger, Mihai-Andrei Dragnea, Natraj Ekambaram, Sebastian Grigore, Doru Gucea, Michal Hanak, Mathieu Imbault, Saleem Kala-Janssen, Prabhu Loganathan, Nihaar Mahatme, Pascal Mareau, Jason Martin, Guillermo Michel, Sujata Neidig, Ali Osman Örs, Nicu Penişoară, Laurent Pilati, Wim Rouwet, Erich Styger, Marc Vauclair, and Francois Villeneuve. Special thanks goes to the reviewers who helped convey the concepts, including Gowri Chindalore and Monica Davis.

A well-architected edge computing system requires multiple domains of expertise, and these contributors are the experts who are sharing their knowledge and expertise with you. We would love to hear from you about your experiences in this new era of edge computing. Let the journey begin!

#### **Robert Oshana**

Vice President, Edge Processing Software R&D NXP Semiconductors Technical Editor-in-Chief

#### **CONTENTS**

| Foreword                                                                  | 3   |

|---------------------------------------------------------------------------|-----|

| Preface                                                                   | 4   |

| Chapter 1: Introduction                                                   | 6   |

| Chapter 2: Hardware and Software Architectures                            | 14  |

| Chapter 3: Security                                                       | 28  |

| Chapter 4: Machine Learning Intelligence                                  | 50  |

| Chapter 5: Connectivity                                                   | 64  |

| Chapter 6: Device Life-Cycle Management                                   | 104 |

| Chapter 7: Energy Efficiency and Optimization                             | 120 |

| Chapter 8: Human Machine Interface                                        | 140 |

| Chapter 9: Use Cases                                                      | 156 |

| Local Voice at the Edge Optimized for Power Efficiency                    | 158 |

| 5G Technology as an Enabler for Industry 4.0                              | 162 |

| Wearables                                                                 | 169 |

| Time-Sensitive Networking and Distributed Real-time Computing at the Edge | 175 |

| Intelligent Connected Vehicles                                            | 183 |

| Chapter 10: Development Tools                                             | 192 |

| Glossary                                                                  | 204 |

| Contributors                                                              | 209 |

Chapter 1

## EDGE COMPUTING INTRODUCTION

#### THE ROAD TO THE EDGE

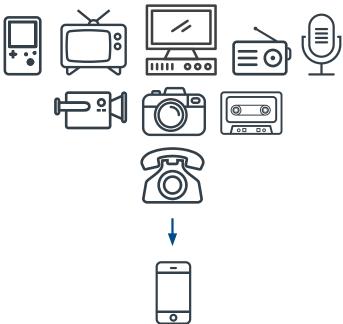

In the "early days" of the internet of things (IoT), processing and most storage was performed in cloud data centers because only the cloud had the computational resources needed to perform complex analysis. But as more connected applications were deployed, the limitations of cloud processing became apparent.

One of the limitations was latency — the time required for the data generated by sensors at the source, to traverse the path to the cloud for processing and then back to deliver actionable results. Milliseconds of latency might not be important in a smart thermostat, but an industrial robot and other real-time systems require even less time for ensuring safety and productivity. For the sensor-based safety features on modern vehicles, latency can be a matter of life and death.

Even a modest application with sensors can create enormous amounts of data that consumes costly bandwidth available across the network. The cloud-based approach could also expose sensitive information, including intellectual property (IP), that must be protected. Today, security has become one of the most critical aspects of the IoT.

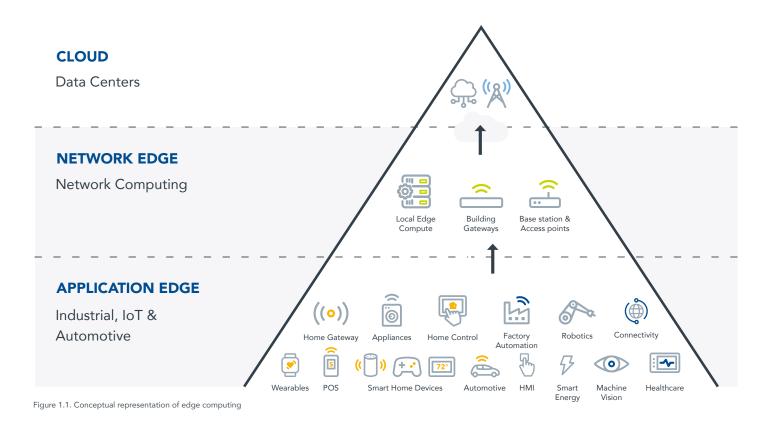

A better solution is to divide the processing tasks between cloud-based servers and processors operating at the location where the data is generated, which is generally called the edge. More precisely, it's the edge of the network, or, from a data center's perspective, the far edge. Note that some processing has always been performed at the edge, principally in gateways that aggregated the data produced by sensors into a standard format, and then sent outward (Figure 1.1).

NXP EdgeVerse<sup>™</sup> edge processing solutions span across IoT, industrial and automotive markets.

However, in this new scenario, significant processing is performed at the edge on processors to satisfy the needs of real-time applications that require responses almost instantaneously. Several solutions emerged to achieve this new scenario.

In the first, mini data centers placed near the end-user location perform reasonably high levels of processing. Because they are nearby, latency is dramatically reduced. In the next approach, the gateway became a more formidable processing element with less computational horsepower but the ability to reduce latency even further. None of these approaches are small or consume little power.

Recent advancements in computing, including applications processors and microcontrollers, have brought significant compute capability to the edge. These devices can now perform machine learning, creating a plethora of edge applications that span beyond gateways and to the sensors and things in between.

#### **TINY POWERHOUSES**

Microcontrollers and microprocessors have made great leaps forward in performance, capabilities and cost reduction. They can include multiple cores dedicated to specific tasks, support several wireless protocols, feature power management and offer other impressive features. Today, they are powerful enough to make decisions based on data aggregated from multiple sensors at the edge.

They can perform analysis that was formerly the sole domain of the cloud, send commands to machines with virtually no latency and transfer only a summary of the information (a much smaller amount) to the cloud. An intelligent door lock, for example, can facilitate unlocking doors when it recognizes a face because it knows the person, and it can store and process the image data locally for a speedier response and enhanced privacy.

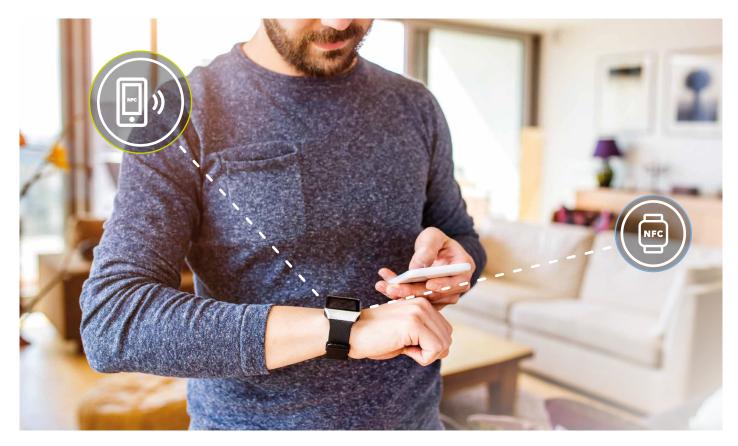

This new approach has become so important for IoT that there's a name for it: TinyML. It shrinks deep learning networks to fit on microcontrollers. The concept is not new. Smartphones have neural networks that enable music identification, multiple camera modes and various other functions to be performed, even in a smartwatch. But only recently has TinyML been applied to edge computing.

#### ENERGY-EFFICIENT COMPUTATION

Many modern MCUs are designed to operate with low power consumption, which enables the devices to run unplugged on batteries for weeks, months and, in some cases, even years while running ML applications on the edge device.

IoT edge devices can run on battery or solar power or be plugged into the wall. Energy is a costly commodity, whether battery or line powered. Computing is not the only consumer of energy; any process involving data aggregation, wired or wireless data transmission and data analysis consumes energy. To understand where to save on energy costs, look at what is consuming it. Decreasing power consumption requires reducing the time that a processor is active. This can be achieved by separating a processor into functional blocks capable of fine-grained power partitioning and management. Edge compute processors are an example of a recent innovation that makes this a reality.

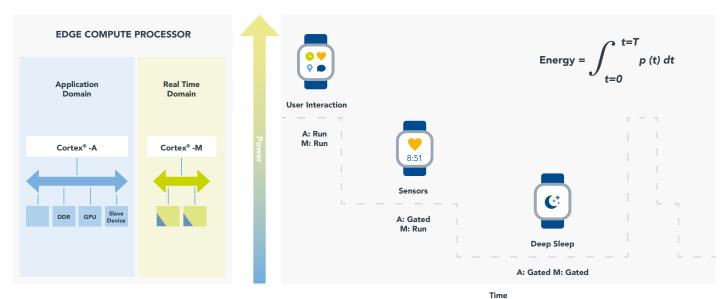

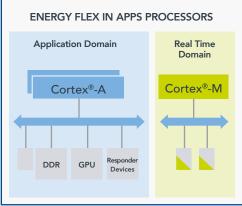

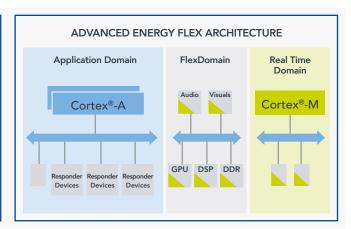

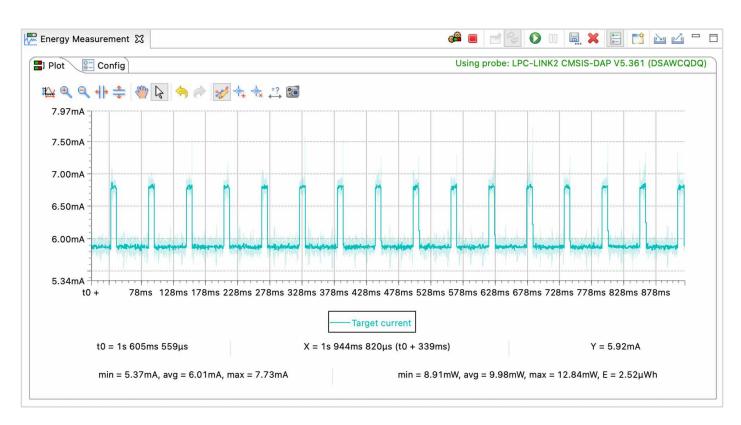

Figure 1.2. Energy-efficient heterogeneous processing

Figure 1.2 shows an edge compute processor application for a smartwatch. In this example, the NXP processor has two separate Arm® Cortex® core domains: a Cortex-A domain for running the watch and a Cortex-M core for real-time processing. Both domains have fine-grained power management and partitioning, allowing the domain to be shut down into a deep sleep mode. Each core's operation is highlighted with the different use cases that show how energy consumption is minimized.

#### INTELLIGENT PRODUCTIVITY

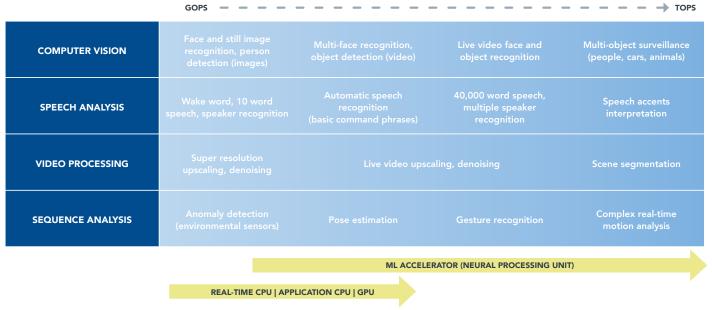

Intelligence and the capability of an edge device to make decisions locally imply the use of ML inference, the basis of an intelligent edge device. This significant rise in ML inferencing at the edge is partly due to the improvements in inference processing techniques and the development of energy-efficient inference "engine" accelerators. The number of potential inference applications that can be conducted at the edge increases with the applications' energy efficiency (Figure 1.3).

Figure 1.3. More possibilities with energy-efficient inference

Potential applications for inference at the edge are limited only by the imagination. Consider a smart home application that monitors for unusual sounds when the occupants are not at home. It detects running water sounds, perhaps indicating a pipe leak or a leaking water faucet. The sound of breaking glass indicates a window being broken. These and many more scenarios trigger the smart home application to alert the owners of problems. In addition to energy efficiency, intelligent productivity adds a societal and safety dimension to the technology benefits.

#### **DATA SECURITY AND PRIVACY**

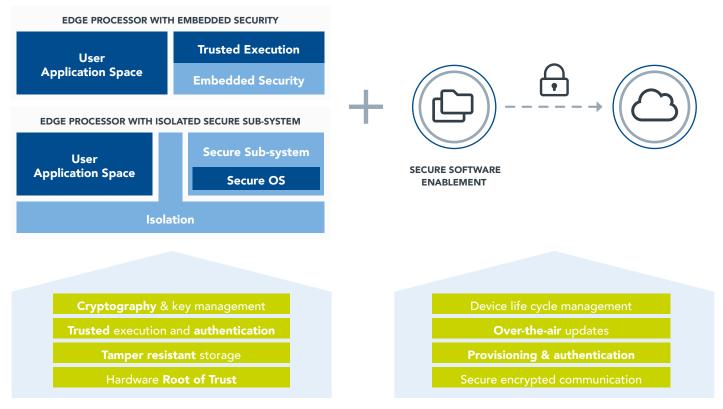

Keeping data secure and private is the number one priority for any application. With more data collected and processed locally, any intelligent edge application needs to remain vigilant. Security applies to securing the edge application code, the data being processed and any data communication to the cloud. The use of encryption keys can help validate firmware, authenticate techniques for cloud communication and prevent adversaries from gaining control of the device. Embedded security, isolated secure subsystems and secure software enablement are the foundation of any intelligent edge processor (see Figure 1.4). Only by taking a holistic approach to device security and data privacy that embraces collective security knowledge and best practices can the IoT transform into the "internet of trust".

Figure 1.4. Typical data security and privacy factors for an edge processor

#### **EDGE AWARENESS**

As edge computing adoption expands, more intelligence will be added to devices to achieve a level of "awareness" across a network of devices. These systems can perform ML, make decisions without any external assistance and use minimal power in a footprint the size of a postage stamp. Connect multiple intelligent devices across a network, and it becomes a data-generating, decision-making aware network.

An intelligent device may process only voice, but intelligent devices across an aware network could combine nuances such as the tone of the voice, facial expressions and body gestures. For example, data from multiple smart home sensors connected across an aware network could recognize danger signals such as someone falling and send an alert to a remote caregiver. And if some of the data must be sent to the cloud, an intelligent edge processor could anonymize it along with other information such as audio profiles of a person's voice and others who are authenticated.

Another example is a home security vision system that scans faces and recognizes family members. A typical security camera captures video of car theft in a driveway. If awareness and context are added, the system can spot a person it doesn't recognize and send an alert to authorities.

Our homes and buildings can also become occupancy-aware, recognizing when the house is empty and then arm the security system, dim the lights and lower the temperature.

#### **SUMMARY**

Computing at the edge is not a replacement for processing in the cloud. Instead, it complements the cloud while providing a way to maintain data safety by keeping it local, eliminating the cost of transmitting gargantuan data to and from a remote data center and allowing real-time applications to get the answers they need in a few milliseconds rather than minutes (or longer). In short, edge computing is now a component of IoT architectures for a vast number of applications.

Credit for the ability to achieve this at low cost with low power consumption must be given to the microcontrollers and microprocessors that have evolved into powerful compute platforms capable of making decisions previously unachievable a few years ago. As their performance increases in coming years, they will take on even more functions to further complement the cloud.

In the chapters that follow, details of edge computing technologies will be discussed in greater detail along with many other technologies that make this approach possible.

### Chapter 2

# EDGE COMPUTING HARDWARE AND SOFTWARE ARCHITECTURES

#### **CONTRIBUTORS**

Edge computing architectures are evolving. This chapter explores the hardware and software that make up these architectures and how they connect the real world with the cloud.

#### **EDGE-TO-CLOUD COMMUNICATION**

Computing advancements have enabled IoT devices to process data locally at the edge without sending data to the cloud. Edge computation can also act as a proxy between the real world and computation in the cloud. End-device sensors collect information from the real world. That data is processed locally (filter and compute), and the resulting meaningful information can be sent to the cloud. Edge computing involves "data in motion," and cloud-based computation involves "data at rest." In that sense, edge computing is enabling communication from the edge to the cloud, so edge computing technology must work with multiple communication protocols and convert these to cloud-based protocols.

Edge computing also is responsible for the business rules of processing data in preparation for transmission to the cloud. For example, an engine sensor emits rotation status multiple times each second, but the analytics in the cloud operate on this data less frequently — once every 30 seconds. The edge computation must prepare the data locally and send it to the cloud every 30 seconds. This is an example of a "smart" gateway, where this intelligence is embedded locally in the edge device.

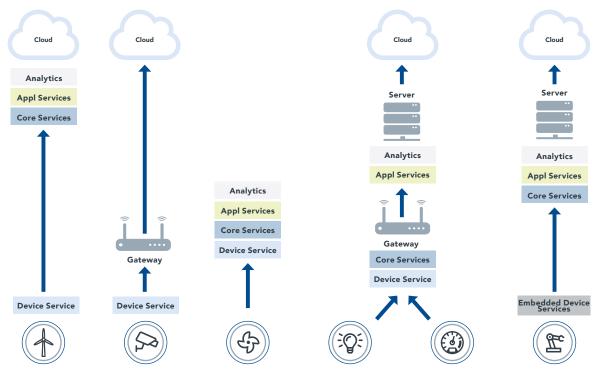

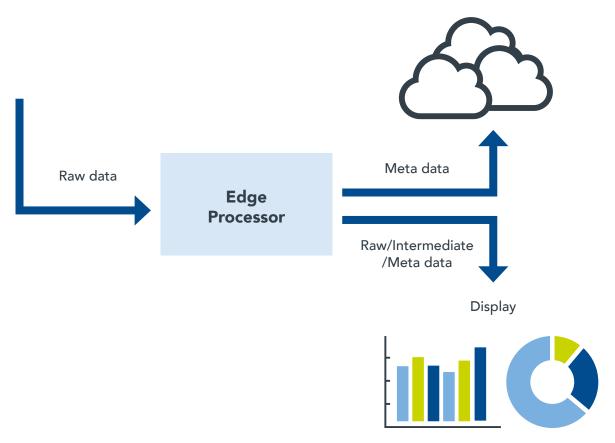

Figure 2.1. Edge computing architecture model

#### **SENSORS AND ACTUATORS**

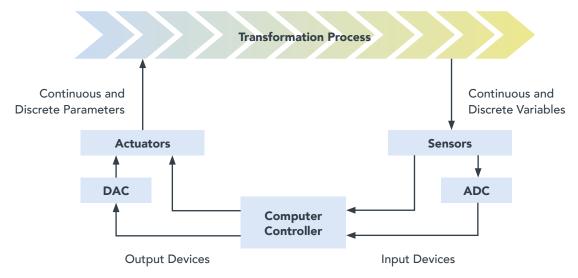

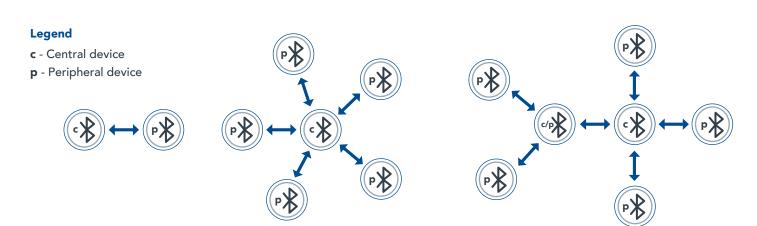

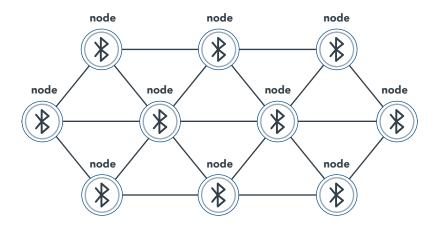

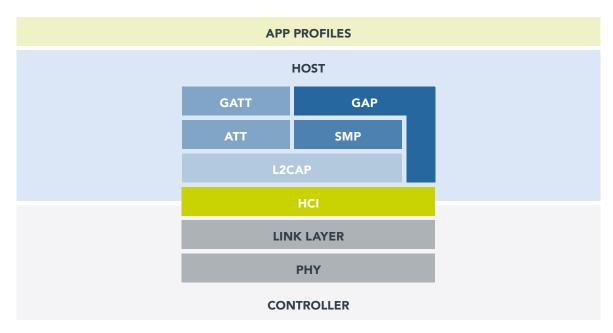

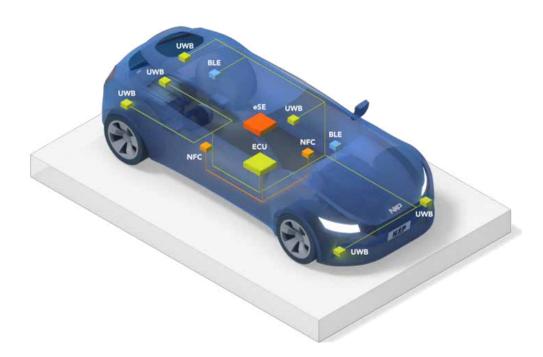

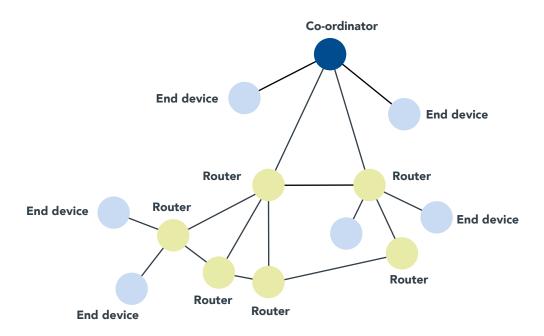

Sensors and actuators (see Figure 2.2) operate in the trenches. They must have robust mechanisms to communicate with each other as well as the gateway and sometimes directly with the cloud. These communication technologies include Bluetooth®, Bluetooth® Low Energy (Bluetooth LE), Zigbee®, Wi-Fi and near-field communication (NFC).

Figure 2.2. Sensors and actuators operating in the real-world environment

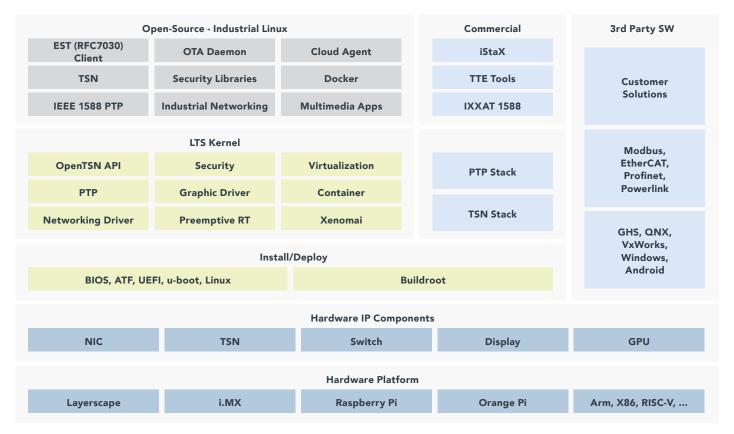

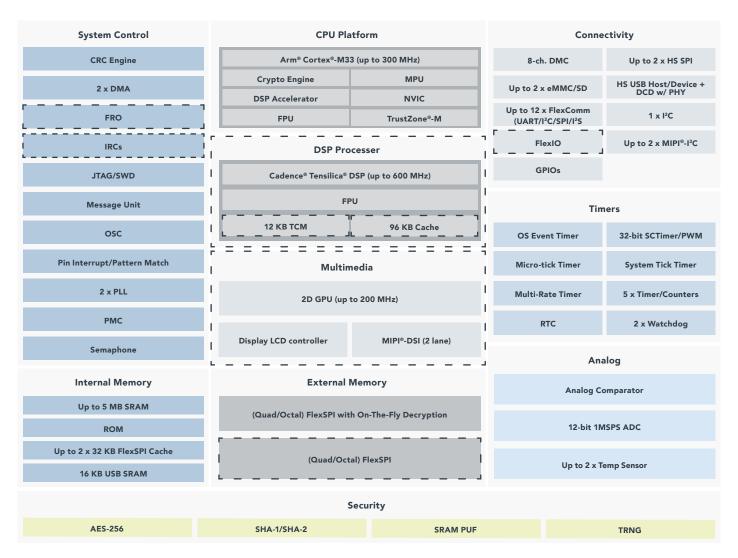

Sensors and actuators in edge computing systems usually communicate with microcontrollers where data is converted (analog to digital and/or digital to analog). Figure 2.3 shows an example of a microcontroller for an edge processing end node. It has a rich set of connectivity, processing and multimedia capabilities. These serve applications that require graphics such as wearables or smart meter systems. The microcontroller also has robust security capabilities to protect data flowing in and out as well as real-time capabilities such as interrupt processing and real-time scheduling.

| System C                   | ontrol                                  | Main CPU Platform                                                                                                                  |                                               |                     |             | Connectivity                 |                   |                                     |

|----------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------|-------------|------------------------------|-------------------|-------------------------------------|

| DC-DC an                   | d LDO                                   | Arm Cortex-M7 (up to 1 GHz)                                                                                                        |                                               |                     |             | ASRC                         | GPIO              |                                     |

|                            |                                         | 32 KB D-cache w/ ECC 32 KB I-cac                                                                                                   |                                               | 32 KB I-cach        | ie w/ ECC   |                              | 3 x CAN-FD        | HS GPIO                             |

| 2 x eD                     | MA                                      | FPU                                                                                                                                | MPU                                           |                     | NVIC        |                              | 8-ch. DMIC        | 6 x I <sup>2</sup> C                |

|                            |                                         | Up to 512 KB TCM w/ ECC                                                                                                            |                                               |                     |             |                              | 2 x eMMC/SD       | 4 x I²S/SAI                         |

| Message                    | Unit                                    | Secondary CPU Platform                                                                                                             |                                               |                     | i           |                              | 2 x EMVSIM        | 8 x 8 Keypad                        |

| PLL, C                     | PLL, OSC                                |                                                                                                                                    |                                               | ı                   |             | 10/100 ENET<br>w/ IEEE® 1588 | S/PDIF Tx/RX      |                                     |

|                            |                                         | 16 KB D-cache w/ Parity                                                                                                            |                                               | B I-cache w         |             |                              | bps ENET w/ AVB   | 6 x SPI                             |

| Resource Dom               | Resource Domain Control    FPU MPU NVIC |                                                                                                                                    |                                               | NVIC                |             | bps ENET w/ TSN              | 12 x UART         |                                     |

|                            | L                                       | =======================================                                                                                            |                                               |                     |             |                              | 2 x FlexIO        | 2 x USB 2.0 OTG w/ PHY              |

| Secure JTAG, SWD           |                                         |                                                                                                                                    | Multimedia                                    |                     |             |                              | Z X FIEXIO        | 2 X 03B 2.0 OTG W/ FITT             |

| Semapl                     | none                                    | 2 GPU with Vector Graphics Acceleration                                                                                            |                                               |                     |             | Timers                       |                   |                                     |

|                            | 1                                       | 2D Graphics Acceleration (PXP) Resize, CSC, Overlay, Rotation                                                                      |                                               |                     |             |                              | 1 EWM             | 4 x Quadrature ENC                  |

| Temp Mo                    | onitor                                  | MIPI® CSI                                                                                                                          | MIPI® CSI Parallel CSI  MIPI DSI Parallel LCD |                     |             |                              | 4 x FlexPWM       | 4 x Quad Timer                      |

|                            | Ĺ                                       | MIPI DSI Paranei ECD                                                                                                               |                                               |                     |             |                              | 6 x GP Timer      | 4 x Watchdog                        |

| Internal M                 | lemory                                  | External Memory                                                                                                                    |                                               |                     |             |                              |                   |                                     |

| Up to 2 MB S<br>Configurab |                                         | Dual Channel QSPI FLASH x2 w/ Encypted Execution<br>HyperRAM™/HyperFLASH™/PSRAM                                                    |                                               |                     |             | Analog                       |                   |                                     |

|                            |                                         | External Memory Controller w/ Memory Crypto Engine<br>8/16/32-bit SDRAM/LPSDRAM 8/16-bit Parallel<br>NAND/NOR Flash/FPGA/SRAM/8080 |                                               |                     |             | 2 x ′                        | 12 b ADC 4.2 Msps | 4 x Analog Comparator<br>w/ 8 b DAC |

| ROM                        | И                                       |                                                                                                                                    |                                               |                     |             |                              | 1 x 12 DAC        |                                     |

| Security                   |                                         |                                                                                                                                    |                                               |                     |             |                              |                   |                                     |

| AES-128/256                | Code Watchdog Timer                     | DES/3DES                                                                                                                           | eFus                                          | eFuse Elliptic Curv |             |                              | НАВ               | Memory Crypto Engine                |

| RSA4096                    | Secure RAM                              | Secure RTC                                                                                                                         | SHA-1/S                                       | SHA-2               | SRAM PUF/UI | DF                           | Tamper Detection  | TRNG                                |

Figure 2.3. Hardware architecture for edge processing using a microcontroller for example  ${\sf Figure}$

#### MICROPROCESSOR AND MICROCONTROLLER BASICS

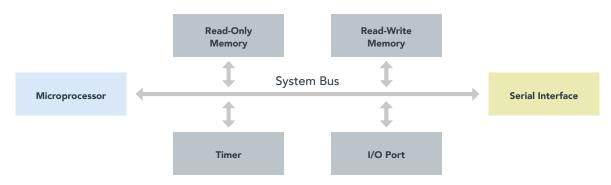

A microprocessor is a general-purpose digital computer central processing unit. To make a complete microcomputer, a number of additional components, including memory (ROM and RAM), interfaces and I/O ports are required, as shown in Figure 2.4.

Figure 2.4 Typical microcontroller software architecture for edge processing

In Figure 2.4, support devices, including read-only memory, read-write memory, serial interface, timers and I/O port are all external and interfaced to the microprocessor via the system bus. The system bus, which connects components of a system, is composed of the data bus to carry information, an address bus to determine its destination or where it will read from, and a control bus to determine its operation. The primary use of a microprocessor is to read data, perform extensive calculations on that data, and store the results in a mass storage device or display the results.

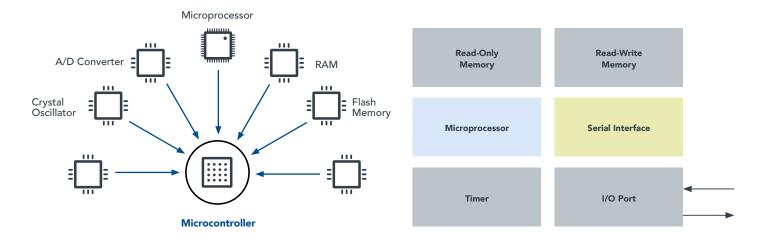

The design of the microcontroller is driven by the desire to make it as expandable and flexible as possible. A microcontroller is a functional computer system-on-a-chip. Microcontrollers include an integrated processor, memory (a small amount of RAM, program memory, or both) and peripherals capable of input and output (see Figure 2.5).

Figure 2.5 Microcontroller based system

Although the microprocessor is considered to be a powerful compute machine, it is limited with how it communicates to the peripheral environment. For communication with the peripheral environment, the microprocessor must use specialized circuits, which are external chips. The microprocessor, by definition, is the heart of the computer. On the other hand, the microcontroller is designed to be all of that in one: No other specialized external components are needed for its applications because all of the necessary circuits are already built into it. This saves both time and space when designing an end device.

Generally in the embedded world, the term "MPU" is used for "microprocessing unit" or "microprocessor" and does not include flash memory in the system-on-chip. Likewise the term "MCU" is used for "microcontroller" and includes on-chip flash memory in the system-on-chip.

#### **EDGE DEVICE DESIGN CHALLENGES**

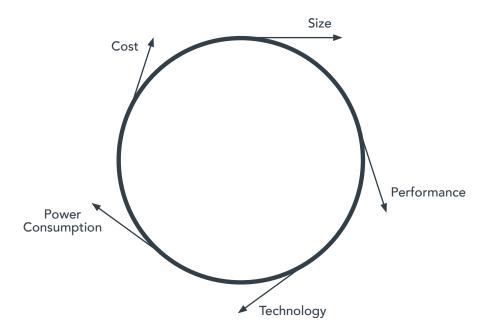

An edge device design must balance numerous design attributes, as shown in Figure 2.6.

Figure 2.6 Parameters that control embedded system success

These design attributes typically compete with one another: improving one often leads to degradation of another. For example, if the die size is reduced, the features and performance of the edge device may suffer. Moving to a lower technology node to reduce the die size and cost, however, may increase the leakage and have an adverse impact on power consumption.

#### **Performance**

Edge device performance depends on more than processor speed. Real-time performance, or how quickly a system reacts to a specific event, is key. An edge device running a real-time operating system (RTOS) would often guarantee a response within specific time frame, which offers determinism. Conversely, the typical response for desktop computing is non-deterministic and guaranteed response time is not critical.

Systems used for many mission critical applications must process data in real-time. The real-time processing fails if it is not completed within a specified deadline relative to an event; deadlines must always be met, regardless of system load.

#### **Power Consumption**

Low power consumption is a critical parameter for an edge device. Compared to typical systems or desktop computers that are always powered, many edge devices are powered by battery. Though this is use-case dependent, an edge device may have a conflicting need for low power consumption and more performance.

Some applications may be continuously powered by battery including water or gas meters that measure the flow of water in a residential or commercial complex. Meters are required to work for several years without replacing the battery. Since they are often idle, ultra-low power modes are often used. Consumption can be measured in sleep mode, and enabled for counter overflows or data transmission to a remote network or cloud.

#### Technology, size and design cost

Unlike the desktop world where performance requirements drive the technology choices, there are number of factors that affect that decisions in edge device design. Some edge devices must be highly reliable to operate in extreme conditions for long operational hours without failure. A stable technology node that is well tested under extreme conditions is recommended. Furthermore, it is reasonable to assume that a system-on-chip for an embedded device would include analog-to-digital convertors (ADC/DAC) and integrated power management controllers (PMICs) that are tuned to specific technology. These need to be re-designed every time a new technology node is adopted which adds significant risk and design cost. Further, switching between different technology nodes can impact power consumption of the device and low power modes, affecting the chip architecture.

Since switching between technology nodes adds non-recurring engineering costs, volumes have to be high to justify the decision. To reduce the per unit cost of embedded systems on a chip (SoCs), it is necessary to reduce the die size either by restricting feature set or by switching to a lower technology node, which may be a natural transition once the technology is stable and the transition cost is justified. There is always a fine balance between technology, die size and design cost when determining an SoC for an edge device.

#### **SOFTWARE**

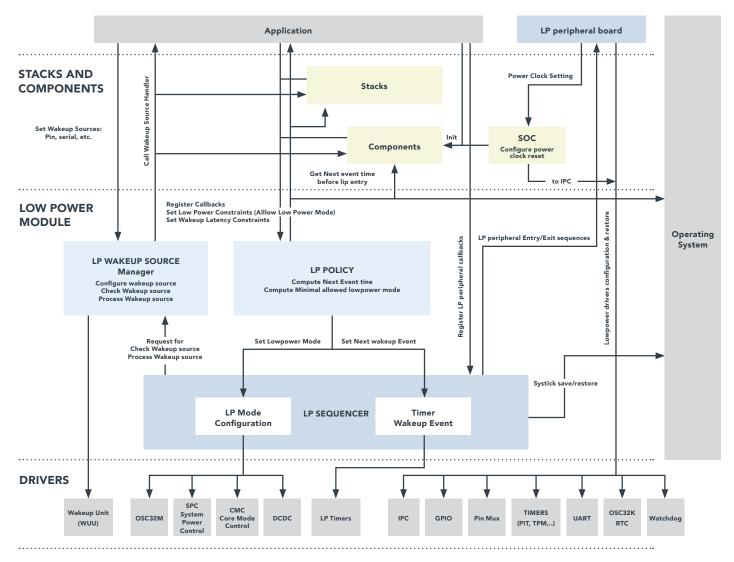

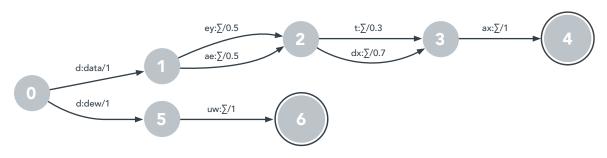

An edge processing microcontroller requires a comprehensive set of enablement software. Figure 2.7 shows a software architecture that features:

| Security                                     | Conne                           | ectivity                         | Application            | Tools/Support              |                       |

|----------------------------------------------|---------------------------------|----------------------------------|------------------------|----------------------------|-----------------------|

| Pre-intergrated and<br>Certified Colutions   | Certified BLE<br>w/ Smartmesh   | ZCLIP/ZCAL on Thread             | NFC Drivers            | USB-C PD Stack             | Config Tools          |

| Crypto Accel<br>Hardware                     | Certified Thread<br>Stack       | uWeave                           | EoU Motor Control      | Touch Sensing              | IDE                   |

| Tamper-Detect<br>Hardware                    | Zigbee Pro                      | HomeKit                          | Safety IEC 60730       | Wireless Charging          | Analysis Tools        |

| Unified TCP/IP<br>CoAP, MQTT<br>6LoWPAN, etc | Secure Ops,<br>Key Mgmt,<br>TEE | Cloud Services<br>Connectivity   | Security -<br>TLS/DTLS | Open Thread,<br>BLE Stack  | Filesystem<br>(FatFS) |

| Peripheral Drivers                           | USB Stacks;<br>emWin GUI        | Crypto HW,<br>TrustZone-M/MPU HW | Radio MAC/PHY          | 802.15.4/SMAC;<br>BLE LLFW | Bootloader            |

Figure 2.7. Microcontroller software architecture for edge processing

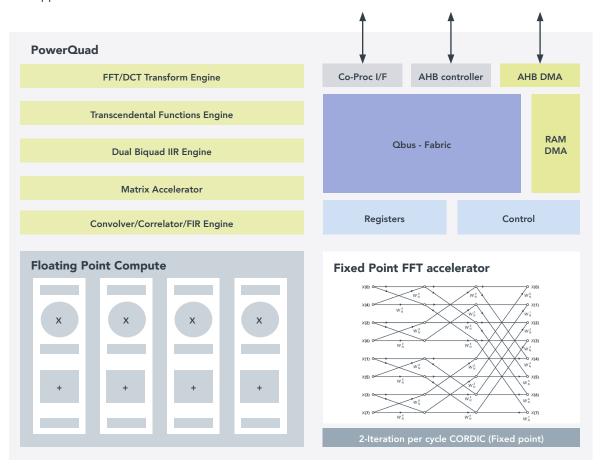

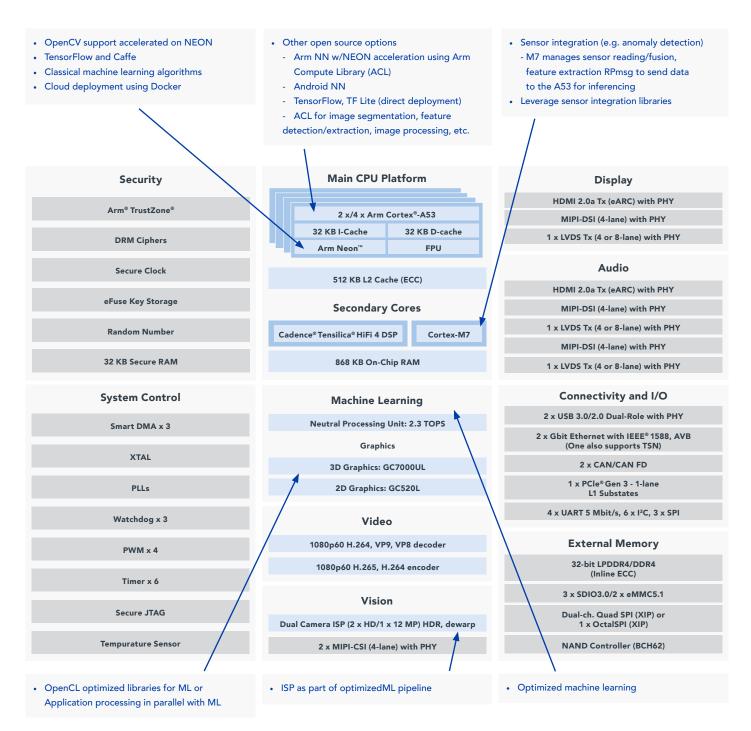

#### ADVANCED PROCESSING

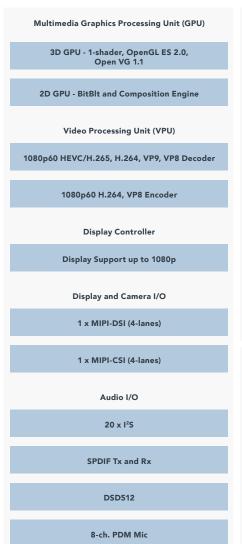

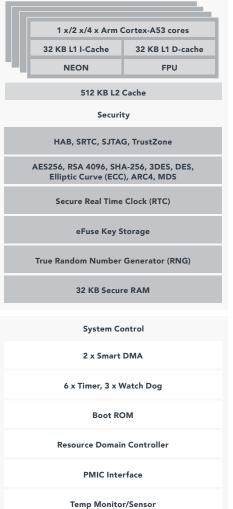

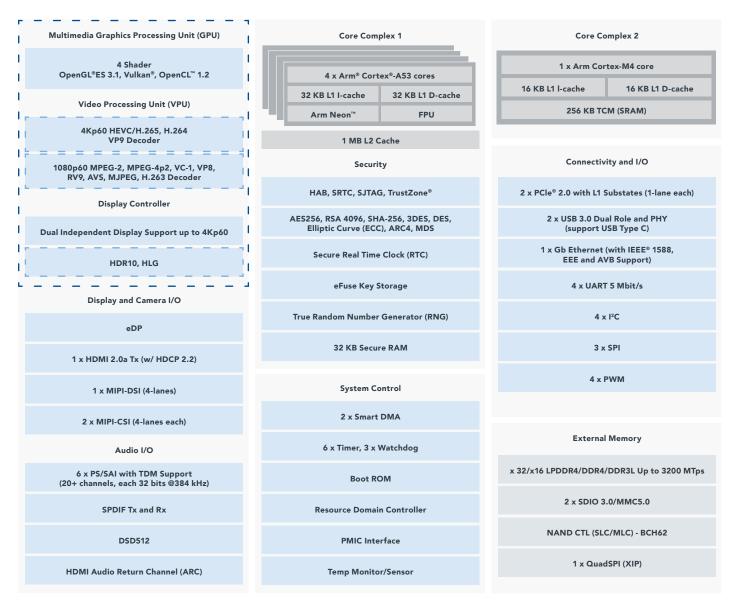

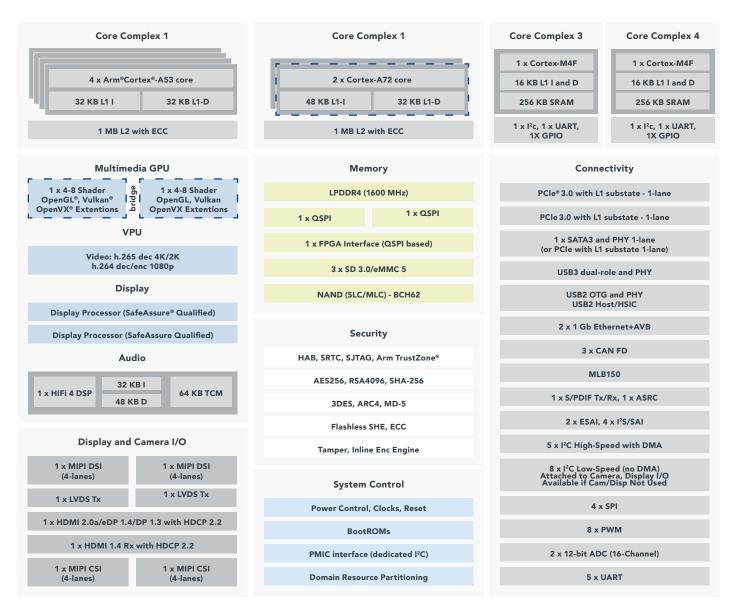

Edge processing often requires more advanced processing capability for the devices operating on the edge and aggregating information from one or more end-node devices. Figure 2.8 shows an example of an edge processing device. This multimedia device has a range of capabilities to support various edge processing application types:

Processing power using multicore technology

Camera, video and audio interfaces

2D and 3D graphics capabilities

Connectivity protocols

Security protocols and performance

ML capabilities

Core Complex 1

1 x QuadSPI (XIP)

Core Complex 2

Figure 2.8. Edge computing hardware architecture for advanced processing

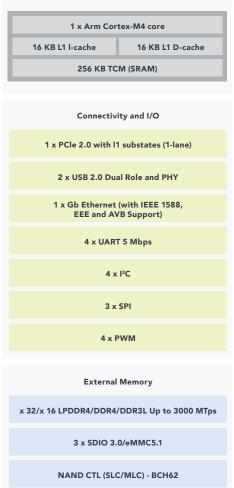

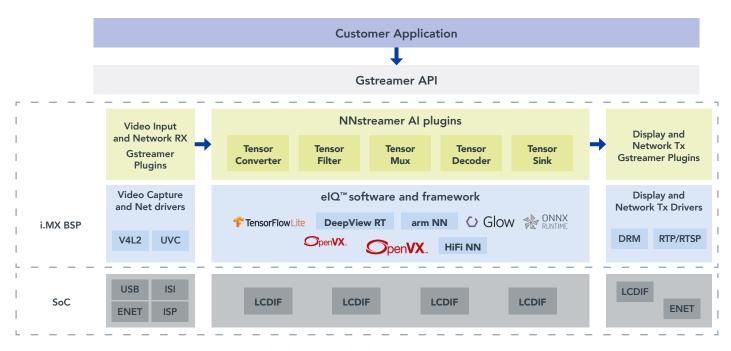

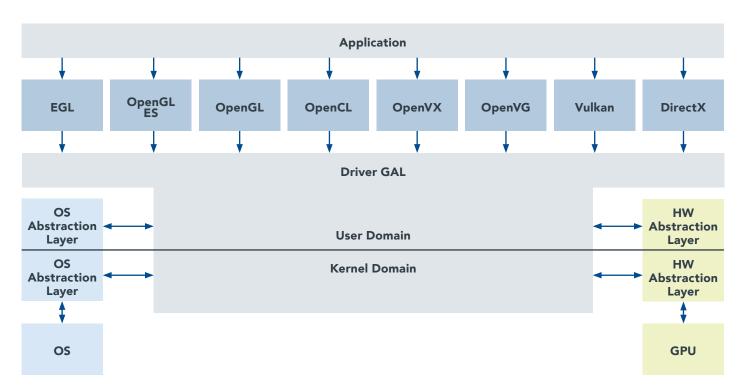

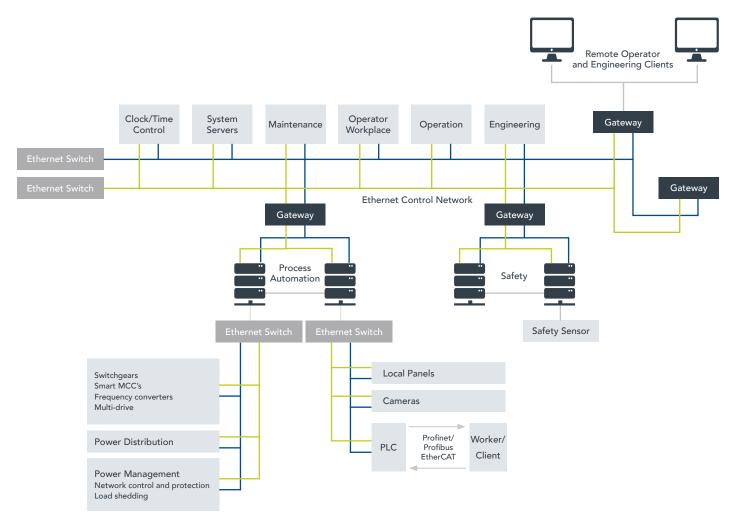

Edge computing devices such as the one shown in Figure 2.8 require more advanced software enablement. Figure 2.9 shows a software architecture common in many edge processing devices. This architecture contains rich OSs such as Linux® and Android, and software enablement for the advanced hardware capabilities shown in Figure 2.8.

Figure 2.9. Edge processing software architecture for advanced hardware capabilities

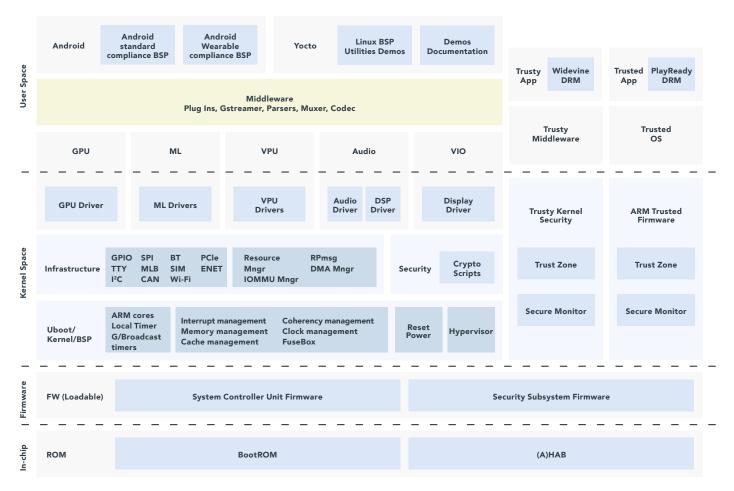

For certain market segments, this software enablement can be customized. For example, Figure 2.10 shows software customized for industrial applications, with support for more advanced industrial protocols such as time-sensitive networking, EtherCAT and PROFINET.

Figure 2.10. Edge computing industrial software architecture

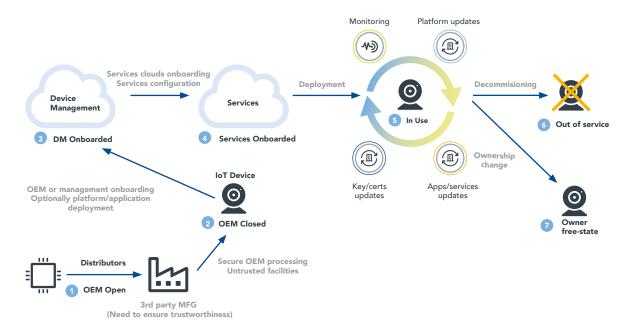

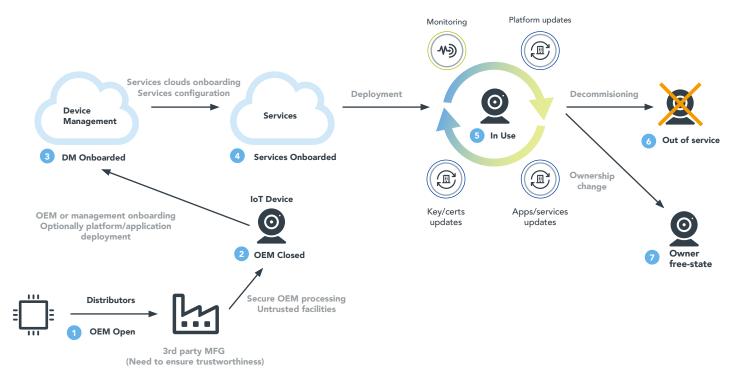

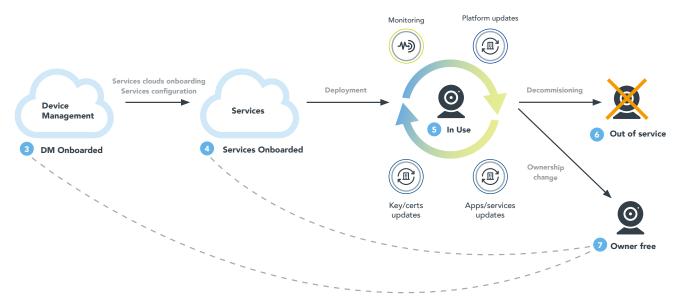

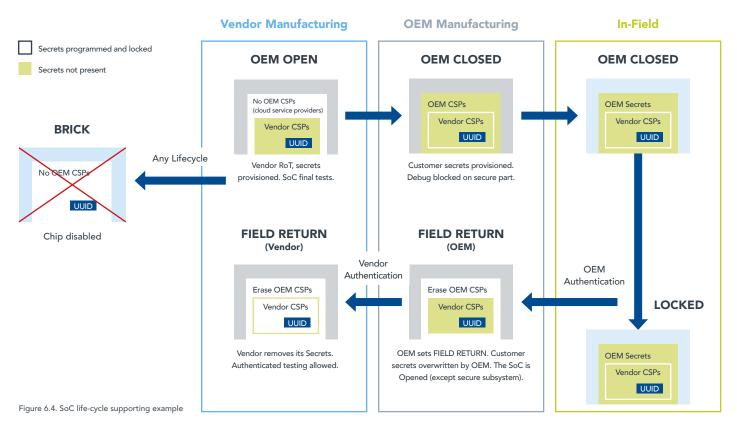

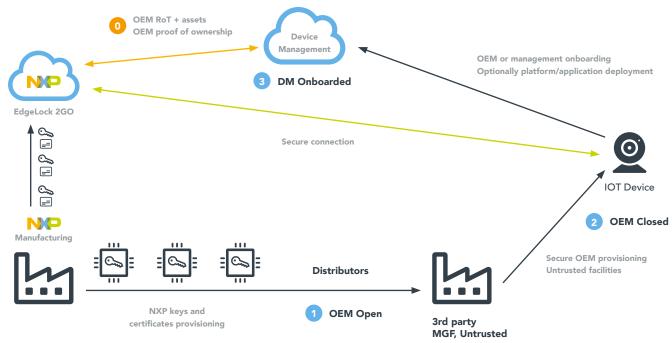

#### EDGE COMPUTING DEVICE LIFE CYCLE

Another important component of an edge processing system is the ability to manage the life cycle of the edge computing devices deployed in the field. This includes:

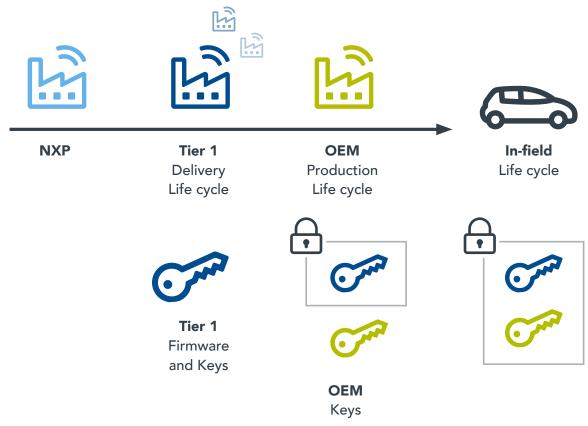

Figure 2.11 shows a high-level flow of this device life-cycle management process. See Chapter 6 for more details on life-cycle management.

Figure 2.11. Device management in an edge computing environment

#### **OPEN-SOURCE EDGE COMPUTING**

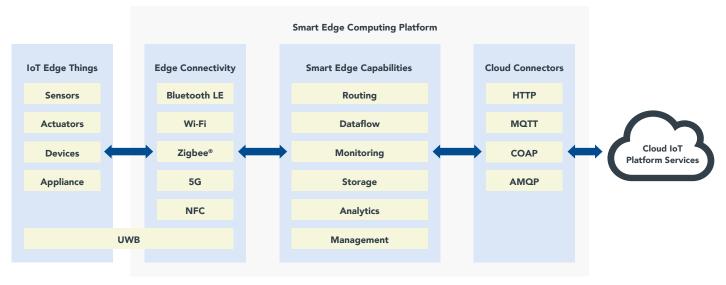

In addition, some open-source edge computing platforms support general edge computing applications. An example is EdgeX (see Figure 2.12), which is vendor-neutral software that interacts with the capabilities in the real world (sensors, actuators and other objects). It's essentially a middleware layer that manages physical sensing and actuating and the cloud IT systems.

Figure 2.12. The EdgeX open-source edge computing software platform

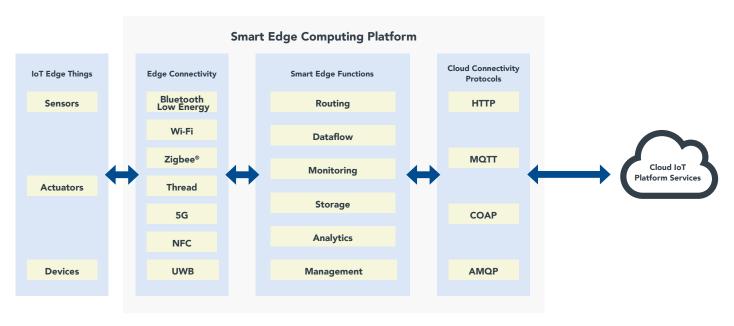

#### COMMUNICATION PROTOCOLS FOR EDGE COMPUTING

Once data is at the edge, messages must be organized via protocols before communicating with the cloud. These "cloud" protocols include Message Queue Telemetry Transport (MQTT), Advanced Message Queuing Protocol (AMQP), Constrained Application Protocol (CoAP) and, of course, Hypertext Transfer Protocol (HTTP).

Edge computing also requires a rich set of run-time capabilities. One category referred to as "dataflow" includes receiving and processing sensor data using the communication protocols in the previous paragraph. Once data is received from the sensors and end node devices, it is filtered, cleansed and transformed using various control protocols and then aggregated, among other things.

For example, in a smart building application, temperature sensors distributed throughout the building send temperature information to the edge device using the Bluetooth LE communication protocol. Software functions on the edge device implement business rules that determine, based on the received data, that the air conditioning must be turned on.

The software function sends air temperature commands to the air conditioners using the Zigbee communication protocol. Temperature information is also sent to the cloud for general analytics purposes. The edge computing software also does this using a cloud-based application programming interface (API) call.

Security constraints, such as authentication, must be applied as well.

#### **DECISION-MAKING AT THE EDGE**

Many decisions must be made close to the device for latency and security reasons. Sending information to the cloud for every decision is not practical. A more obvious example of this is real-time anomaly detection on a factory floor. This capability helps manufacturers adjust robots to optimize production capacity and yield as well as to identify potential defects as soon as possible so that any affected equipment can be removed and serviced immediately. This is usually implemented using reactive monitoring, which is different from the broader function of data analytics, a mostly passive and non-real-time process.

Many other applications featuring "independence from the cloud" offer these same benefits. EdgeX has four middleware services:

Supporting

Application

Device

This framework can be used with the device architectures mentioned earlier in use cases including:

Smart building optimizing efficiency across facility

Factory automation interoperability across sensors, machines and robots

Water treatment loss detection in real-time

#### **SUMMARY**

Edge computing essentially offloads computation and storage from a centralized cloud to the network's logical extremes. Edge architecture is a distributed computing architecture that includes both hardware and software. Edge devices can connect to other edge devices and may ultimately connect to a centralized system or cloud. In addition to the hardware, communication protocols, enablement software and device life cycle management are important factors to edge computing architecture.

## Chapter 3

## EDGE COMPUTING SECURITY

#### **CONTRIBUTORS**

Silvano Di Ninno, Security Software Engineer, NXP Semiconductors

Nicusor Penisoara, Senior Director, Security, Graphics & Machine Learning Software R&D, NXP Semiconductors

Marc Vauclair, Senior Security System Architect, Technical Fellow, NXP Semiconductors

The security of edge devices is increasingly important as more of them are incorporated into systems. This chapter explores functional and platform security methods to address weaknesses pinpointed by risk assessments conducted during the design stage.

#### **SECURITY: A HOLISTIC SYSTEM PROPERTY**

Future systems will encompass billions of interconnected devices. They will form an attractive target for attackers. Edge devices are part of these systems. They process data closer to where it is generated while connecting with remote and cloud-based services. They collect raw data from sensors, analyze and extract relevant information to be delivered to the cloud and present it to local users. In most cases, this information contains sensitive data that needs to be protected. Also, some edge devices have actuators to control utilities and machinery that can be misused; therefore, the commands received from remote services need to be verified as authentic and originating from the proper controlling entities. This makes them interesting targets for the attackers.

Security is a holistic system property<sup>1</sup>; security is not an add-on. A system is as secure as its weakest component that an attacker can reach. Edge devices will play several roles in system security:

Edge devices are privileged targets (the return on investment for an attacker is higher for an edge device controlling many devices), and these devices have to be protected accordingly.

They can help improve system security by providing the necessary isolation of less secure subsystems or by delivering secure services to them.

Most of the fundamental concepts used to secure networking devices work for securing edge devices as well:

- Data in transit

- Data at rest

Access control mechanisms

However, although a data-center infrastructure (where cloud services are typically deployed) offers inherent physical protection for the data being stored and processed, edge devices are placed in locations where little or no physical protection is guaranteed. This implies that additional protection and some level of intrusion-detection capability needs to be deployed for edge devices. At the system-on-chip (SoC) level, these needs must be supported by the following hardware capabilities combined with specific software mitigation techniques that protect and react against such attacks<sup>2</sup>:

- Root of trust (RoT)

- Tamper detection

- Secure boot

- Secure enclaves

The edge device and its data protection capabilities make up one critical part of the edge computing security story, but protecting the network and cloud services from edge devices transformed into remote controlled weapons is also important. Edge devices need to process increasingly larger amounts of data in a variety of new ways. To address that, both compute power and the available network bandwidth have grown over the years. This trend will only continue with the emergence of edge artificial intelligence (AI) and the deployment of 5G and faster Wi-Fi technology. Given the ever-tighter interaction between edge devices and the cloud infrastructure, the risk of disrupting the cloud's services is increasing through the following methods, among others:

**Device cloning**

Denial of service (DoS) attacks

Mirai, a malware able to command and control hundreds of thousands of devices to mount denial of service (DoS) attacks, and its variants have inflicted massive damage multiple times recently.

The security for edge devices is two-fold<sup>3</sup>:

- Functional security These security primitives (most of the time the cryptographic features) ensure

that sensitive data remains secure (confidentiality, integrity, authenticity) and private when required.

For example, using encrypted messages between two edge devices is a functional security feature.

- Platform security These security primitives ensure that the implementation of the functional security remains secure in the presence of remote or sometimes local attackers. For example, protecting the secret key used to encrypt and decrypt messages in each of the two communicating edge devices is a platform security feature (one potential implementation of this security feature is secure storage with access control and isolation so that remote attacks on other parts of the software of the edge device under attack cannot recover this secret key). But if local attacks (i.e., those with physical access to the edge device) are considered part of the threat model, more advanced hardware security features such as side-channel and fault-attack resistance should be implemented.

For both kinds of security, some fundamental cryptographic features can be used to secure edge nodes. Through cryptographic protocols and key management techniques, in-transit and at-rest data can be protected and the edge device booting and running authentic, authorized firmware and software can be ensured. Additionally, a unique identity for a device can be constructed to verify and protect it on the edge device side while using it on the cloud infrastructure side for access control. This unique identity can help detect if a device was corrupted and needs to be isolated to avoid DoS attacks.

The ability to create and protect multiple software execution environments on a single SoC is another key functionality required on more advanced edge computing devices. It's needed to isolate sensitive software processing. To integrate applications with third-party software stacks as part of an edge computing offering, secure communication between those different software stacks must be guaranteed.

Finally, security features and countermeasures need to be seamlessly integrated into software stacks so they can be deployed easily by applications running on the edge device. Using a standard and/or well-established open-source application programming interface (API) is essential to maximize software reuse.

#### **CRYPTOGRAPHIC FEATURES**

Cryptographic features<sup>4</sup>, relying on cryptographic algorithms, ensure functionality by providing one or more of the following capabilities in a system:

**Integrity** — The data received is identical to the data sent.

Confidentiality — A third party listening to the communication cannot understand the message.

**Authenticity** — The receiver of a message can verify the authenticity of the message.

Nonrepudiation — The sender of a message cannot deny having sent it.

| Algorithm                  | Integrity | Confidentiality | Authenticity | Nonrepudiation |

|----------------------------|-----------|-----------------|--------------|----------------|

| Hash                       | <b>/</b>  |                 |              |                |

| Symmetric cryptography     |           | <b>✓</b>        |              |                |

| MAC                        | <b>/</b>  | <b>/</b>        |              |                |

| Public key<br>cryptography | <b>~</b>  | <b>\</b>        | <b>/</b>     | <b>~</b>       |

Table 3.1. Security properties of algorithms

#### **HASH FUNCTION**

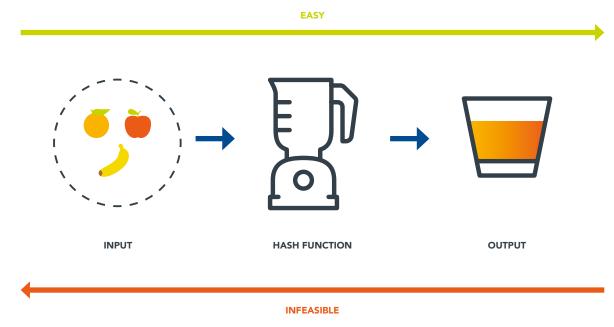

A hash function is a cryptographic function that can take any amount of data as input and provide a fixed number of bits as output. It is a function (see Figure 3.1) for which generating the output from the known input can be achieved fairly easily, while retrieving the input data based only on the output result is infeasible. Another property is that easily creating two different input data points that give the same output result is infeasible as well.

Figure 3.1. Hash function one-way property

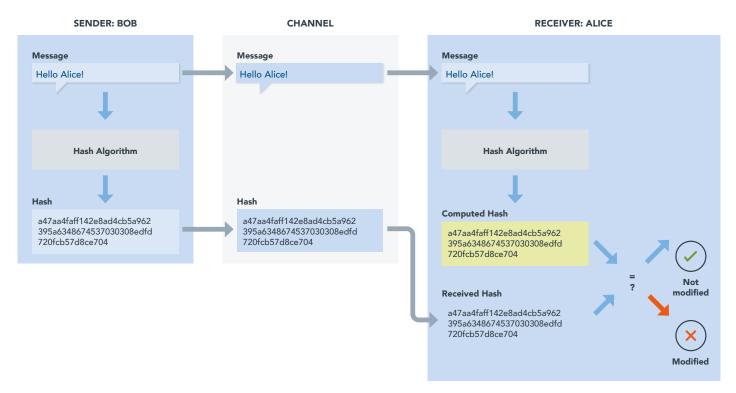

Figure 3.2. Use of hash function to guarantee the integrity of messages

This function is often used for the following (see Figure 3.2):

#### Integrity checking

This use validates that the data received was not corrupted. The common example is a file transfer or a download from the internet. Downloaded files are sometimes associated with the results of a hash function run over the content of the file, for example, the outcome from the sha256sum hash command. The user downloading the file can run the same type of hash function with a downloaded file as an input. The user then compares the output with the sha256sum value contained in the file that was associated. If there is a match, it is highly probable the data wasn't corrupted.

#### User password storage

Storing passwords on a server is potentially dangerous; passwords can be lost if the server is hacked. Instead of storing the password in plain text, the hash of that password with additional fixed data (known as "salt;" the salt is added to prevent rainbow dictionary attacks) is stored. When the user is prompted to enter the password, the same process is used (the verifier software collects the password from the user, collects the associated salt from the system and computes the salted hash of the password), and the resulting salted hash is compared with the data stored on the server. For additional user protection, the user password never appears in plain text on the server.

#### Signature generation and verification

Unlike integrity checking, here the hash function result, in association with other cryptographic operations, is used to validate not only the data's integrity but also the origin of the data. These cryptographic functions used alongside the hash function are part of the public key cryptography. See the "Public Key Cryptography" section later in this chapter.

#### **Proof of work**

Bitcoin uses a hash-based mechanism as proof of work.

Several hash functions are available. Some like MD5 and SHA-1 are considered obsolete and weak. They should be avoided, although some are still used for weak file integrity checking or file identification. In these cases, don't rely on MD5 of SHA-1 for authenticity. As of today, the standardized and recommended functions are the ones from the SHA-2<sup>5</sup> families; these are mandatory if used for signature and signature verification.

#### SYMMETRIC KEY CRYPTOGRAPHY

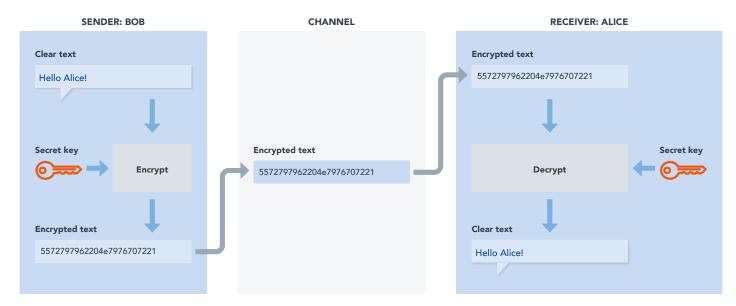

Symmetric key cryptography (see Figure 3.3) uses a secret key shared by the sender and receiver to encrypt and decrypt data. In other words, Alice and Bob use the same key both for encryption and decryption. This function involves relatively fast operations, so users prefer it when exchanging significant amounts of data. The main disadvantage of this function is that the secret key used to encrypt/decrypt data (i.e., the symmetric key) must be shared between the communicating parties appropriately to ensure it does not fall into the wrong hands. Securely generating and sharing a symmetric key is problematic when exchanging data between two remote parties. This problem is exacerbated when confidential information sharing among a larger number of participants is needed. Also, the base encryption/decryption function provides only data confidentiality. This function is often used alongside public key cryptography for key distribution and authentication functions for integrity verification. The AES<sup>6</sup> family (AES-128, AES-192, AES-256) is the most common among the many symmetric key algorithms.

Figure 3.3. Use of symmetric key cryptography to ensure the confidentiality of messages  ${\sf Sim}$

Symmetric key cryptography is often used in the following cases:

#### **Protecting data at rest**

This is used when the data is not moving from one system to another; instead, it's in physical storage such as a hard disk or a flash drive. Data is encrypted so it's protected when the system is off and the data is not being used. On a Linux® OS, dm-crypt can be used for this purpose; on a Windows® OS, BitLocker can be used. Recent SoCs provide on-the-fly automatic encryption and decryption as it loaded or saved to the various memory areas (RAM, flash and so on). For this purpose, the Prince algorithm is used because it has low-latency properties that do not introduce delays in memory accesses.

#### Wrapping keys

This use case is similar to protecting data at rest, but the data protected is another key (i.e., the data stored or transmitted is a secret key encrypted with another secret key). Selecting an algorithm stronger or a key longer than the algorithm associated with the wrapped key or the length of the wrapped key, respectively, is important when wrapping keys.

#### Protecting data in transit

Data exchanges between two or more systems are usually implemented through a connection using a communication protocol on wired (e.g., Ethernet) or wireless (e.g., Wi-Fi) network links. In this case, protocols commonly used are Internet protocol security (IPsec), transport layer security (TLS) or secure shell (SSH). But the connection also can be local within a system, such as an SoC connected to a secure element or trusted platform module (TPM) through an I<sup>2</sup>C interface. In this case, a specific protocol (sometimes a proprietary one) is used.

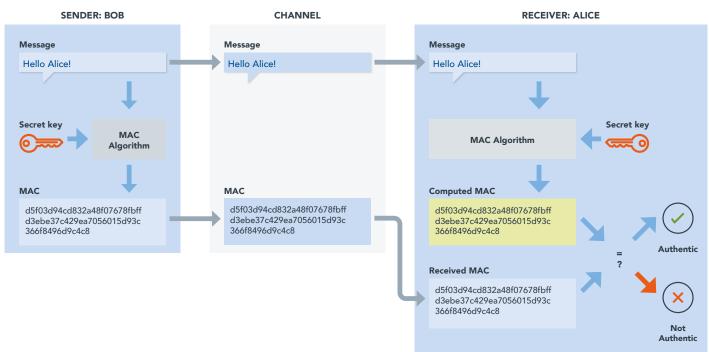

#### MESSAGE AUTHENTICATION CODE ALGORITHM

The message authentication code (MAC)<sup>7</sup> algorithm is a cryptographic function for integrity and authenticity checking. This function is like the hash function with the addition of a shared secret key (see Figure 3.4). Anyone can verify a hash, but only the ones who know the shared secret can verify a MAC. MAC algorithms are categorized in two families: hash MAC uses one of the hash algorithms as an underlying function for the operation, and cipher-based MAC uses symmetric key cryptography (e.g., Advanced Encryption Standard or AES) as an underlying function.

Figure 3.4. Use of MAC to guarantee the authenticity of a message

This function is often used for the following:

#### **Data in transit**

MAC algorithms are commonly used alongside a symmetric cryptography algorithm to authenticate the data being exchanged. This is the case for the network protocol IPsec or TLS. It also can be used locally within a system, for example, the connection between an SoC and an enabled multimedia card (eMMC) chip. To read and write to eMMC storage, a specific protocol is used, and frames are exchanged between the SoC and the physical storage for reading and writing data. In a recent version of the eMMC specification, a special partition was introduced for security purposes. A replay protected memory block (RPMB) and the frame sent and received are protected by an authenticated field. The key used to generate the MAC is stored in the eMMC chip, and only the software in the SoC knows that the key can read and write data in that RPMB partition. Modern protocols use Authenticated Encryption with Augmented Data (AEAD) algorithms that combine the MAC computation with the encryption computations to simultaneously provide confidentiality and authenticity in one operation (e.g., AES in CCM).

#### **Key derivation function (KDF)**

A MAC algorithm also can be used as the underlying function to derive a new key from an existing one. This is a desirable feature in secure systems that requires a key being used only for one purpose (e.g., a key used for encryption cannot be used for authenticity). A simple representation of this function is "KDF (IKM, salt)." KDF is the function for the derivation. It can be, for example, an HMAC function using an SHA256 algorithm. The input key material (IKM) is the secret part of the input function (typically an existing secret key). The salt is a nonsecret input data point. The key derivation technique is frequently used in resource-constrained devices where a single secret key (the IKM) can be stored in fuses — embedded in some ROM in SoC die or a combination of both — and used to generate other keys for a variety of purposes in the system.

# PUBLIC KEY CRYPTOGRAPHY (ASYMMETRIC CRYPTOGRAPHY)

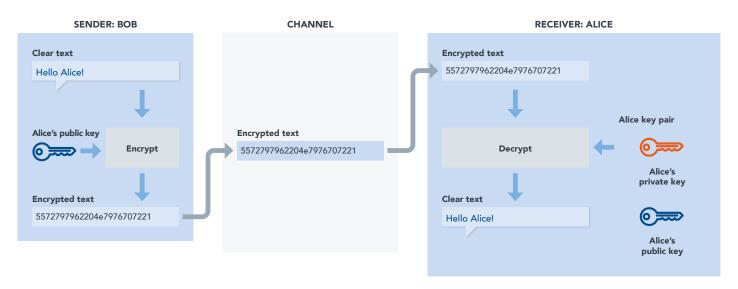

Figure 3.5. Use of asymmetric cryptography to protect the confidentiality of small messages

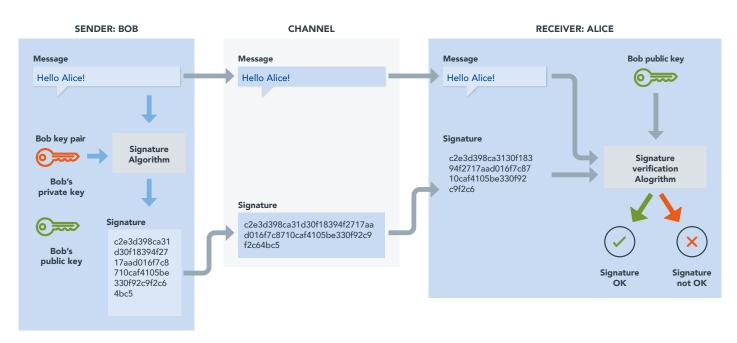

Figure 3.6. Use of asymmetric cryptography for digitally signing messages  $% \frac{1}{2}\left( \frac{1}{2}\right) =\frac{1}{2}\left( \frac{1}{$

As opposed to symmetric key cryptography that uses a single key for both encryption and decryption operation, asymmetric cryptography, which is also known as public key cryptography (PKC), is using a key pair. Each participant has a key pair made of a private key (only known by the owner of the key pair) and a public key (known by all participants). Those keys can be used in different ways. The following two major uses of asymmetric cryptography are illustrated in figures 3.5 and 3.6.

#### **Encryption to provide integrity and confidentiality**

A participant encrypts a message using the public key of the intended receiver of the message, and only the intended receiver is capable of decrypting the message using their private key. For example, the Rivest-Shamir-Adleman (RSA) encryption algorithm can be used for this purpose.

#### Digital signature to provide authenticity and nonrepudiation

A participant signs a message using their private key and sends the message together with the signature. All other participants can verify the signature using the public key of the sender. For example, the RSA algorithm and an Elliptic Curve Digital Signature Algorithm (ECDSA) can be used for this purpose. As mentioned earlier, the digital signature algorithm relies on a hash function; it is the hash of the document that is signed.

PKC has solved the fundamental problem of allowing two entities that have never been in contact before to establish an authentic and confidential message exchange between them.

The PKC function is more computationally intensive than the symmetric functions, so it is commonly used to process small amounts of data and support the following use cases:

- Establishment of communication channels The digital signature capability allows participants

to identify the parties in the communication, while the encryption capability is used as part of a

key-exchanged mechanism to agree on a new key to be used later for the communication.

The TLS protocol is an example of this usage.

- Secure boot mechanism The digital signature is used to authenticate that a binary is genuine. The manufacturer signs the software using their private key and distributes their public key so that any other entity can verify the genuineness of the software.

- Public key infrastructure (PKI) When PKC is used, the identities of the participants need to

be bound to their public keys and the freshness of those keys needs to be ensured. This is the

role of PKI: to certify these links by emitting certificates and revocation status information.

See the "Public key infrastructure" section later in this chapter.

- Attestation services Device attestation means that a device has been provisioned by the

manufacturer with a key pair unique to the device. Whenever an entity of the network in which the

device is connected wants to challenge the device for genuineness, the entity can send a challenge

to the device and the device can send back a signature of the challenge proving the knowledge of

the right private key and, therefore, their genuineness.

#### HARDWARE ACCELERATION

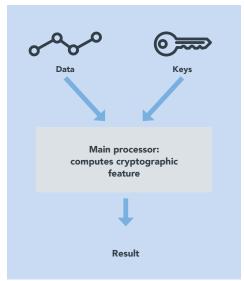

#### SoC without hardware acceleration

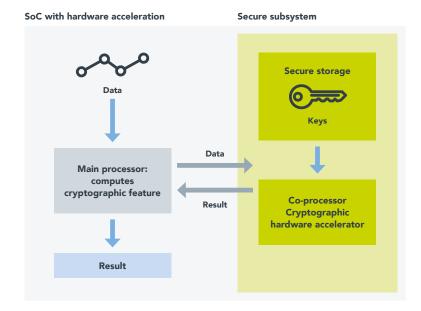

Figure 3.7. Hardware acceleration

With hardware acceleration, an application can offload certain computing tasks to specialized hardware components within the system. To optimize performance and keep the power budget low, the cryptographic functions discussed earlier are often accelerated in hardware on many edge computing devices.

Depending on the edge computing device, one or more hardware accelerators may be available. In some devices, the main core processor is extended with special accelerated cryptographic operation codes; on many other edge devices, one or more additional coprocessors are integrated in the SoC.

For example, the NXP i.MX product family has a hardware IP called the Cryptographic Accelerator and Assurance Module (CAAM) for cryptographic computation hardware acceleration. Beyond the acceleration capabilities, the CAAM offers special key-wrapping functions that protect sensitive keys from being exposed. This key-wrapping mechanism relies on a collection of fuses that are not accessible by the main core of the SoC. This implies that even if an attack succeeds in corrupting the behavior of the main core, the attackers don't have access to the wrapped keys because they don't have access to the internal mechanisms of the CAAM. The key store constructed around these functions is not accessible by the main core of the SoC even if the software running on the SoC is compromised.

Cryptographic hardware accelerators are also hardware isolation devices. The accelerator has its own processing unit, including registers, and its own local memories. These resources are not directly accessible by the other cores in the SoC.

The use of hardware accelerators, which come with device drivers, is integrated in cryptographic software libraries to abstract the cryptographic computations from the point of view of the application software.

Hardware accelerators also provide a guaranteed and sometimes certified implementation of the various cryptographic algorithms. In addition, they can incorporate additional security countermeasures to prevent side-channel attacks or fault-injection attacks that are trying to access the cryptographic credentials used during the cryptographic computations.

#### HARDWARE RANDOM NUMBER GENERATORS

The security of many security primitives and, more specifically, many cryptographic algorithms and protocols relies on the true randomness of some of the data processed during the computations. For example, a network protocol for a secure channel is secure only if the challenges sent between the communicating parties are truly random (if that's not the case, an attacker can guess the session keys and listen to the communication). The digital signature of a message using the ECDSA is valid only if the ECDSA can rely on a truly random number during the signature computation (if that's not the case, an attacker can guess and compute the private key of the signer and forge new signatures in their name). The only way to produce truly random numbers is by the addition of a hardware true random number generator (TRNG). This generator is used by the software. Modern SoCs incorporate a hardware TRNG that's accessible through protected interfaces. The TRNG is mostly used to seed a pseudorandom number generator because the amount of entropy generated by a TRNG per time unit is limited while some protocols require more random material per time unit.

#### PUBLIC KEY INFRASTRUCTURE

A Public Key Infrastructure (PKI) defines and certifies the binding between public keys and entities, individuals and/or organizations. It facilitates the exchange of data between two or more entities that are using PKC by introducing one or more third parties that can attest the identities of those entities and the relationship to the public keys they advertise. This topic is becoming more relevant in edge computing because in some architectures, edge devices can act as these third parties. They have the necessary implementation security features that ensure they cannot be abused.

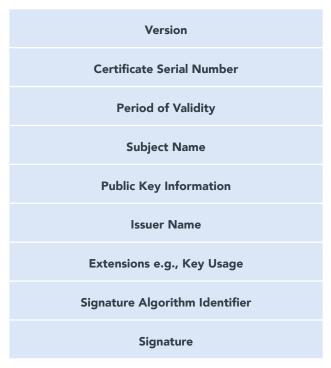

A digital certificate can be used to represent this binding between an identity and a public key. The most common is the X.509 v3 certificate<sup>8</sup>. As shown in Figure 3.8, it contains information about not only the identity of the organization linked to the key pair but also who has issued and signed the certificate as well as a validity period.

Figure 3.8. Example of x509.3 certificate content

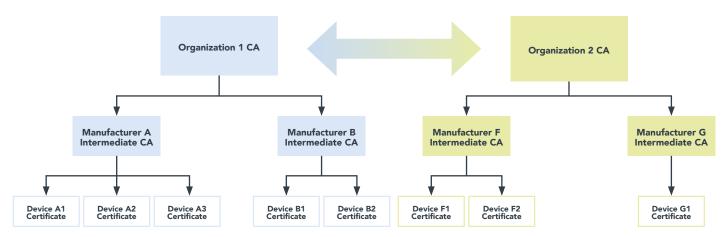

The issuers of those certificates are called certification authorities (CAs). A CA is responsible for checking the link between an identity and a public key along with additional information before it emits a digital certificate. Either the certified entities receive these certificates or the certificates are published in public repositories accessible by anyone. When another entity receives a certificate, it can verify the validity of the certificate thanks to the knowledge of the public key of the certificate issuer (the CA that has signed the certificate) and the trust that the verifying entity has in this CA. The receiving entity can also check whether the certificate has been revoked between its emission and its current use. Having one CA for all purposes is neither feasible nor desirable for many reasons: scalability, availability, confidentiality and so on. That's why instead of having one CA, a PKI is made of several CAs that are commonly organized in a hierarchy. A top CA certifies subauthorities that, in turn, certify entities. CAs also commonly cross-certify each other's certificates.

Figure 3.9. Example of a PKI infrastructure

Certificates do not have an infinite life; they have a start-of-use date and an end-of-use date. In addition, if for any reason (disappearance of the owner of the certificate, security breach of the private key associated with a public key and so on) the certificate is revoked, the CA publishes this end of validity. If the revoked certificate is presented in a digital transaction, it can be rejected by an entity that first checks whether it has been revoked.

A PKI is a set of hardware and software components as well as defined policies. It provides the following services:

PKIs should not be perceived as a single entity that manages all available certificates. A PKI can be not only a public implementation at a large scale in data centers but also a private, single corporation or even an implementation in a single SoC.

The most common use of PKIs is with secure socket layer (SSL) certificates when browsing the internet with "https" URLs. Edge devices may also use "https" URLs to reach out to the internet. However, device life-cycle management and secure boot are other good examples of PKI use by an edge-connected device.

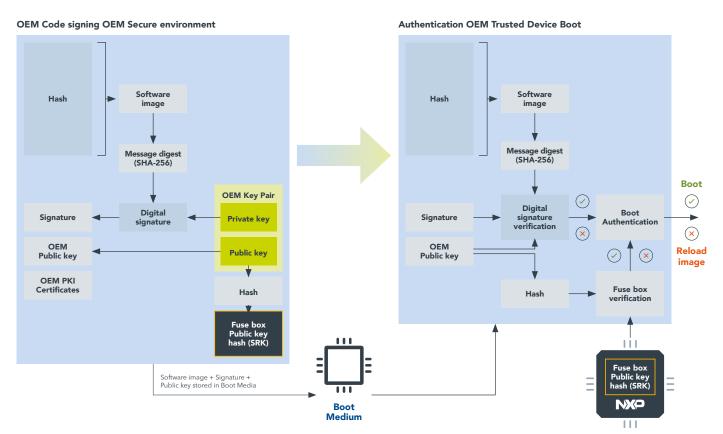

#### **SECURE BOOT: CHAIN OF TRUST**

A key aspect of building a secure system is guaranteeing that genuine binaries are running and that these binaries are trusted by the OEM that owns or supplies the system. The secure boot functionality provides this guarantee. Secure boot typically starts from an immutable memory area within the SoC, which is always inherently trusted and always runs correctly. This immutable part of the SoC and its corresponding features are sometimes referred to as a root of trust (RoT). PKC algorithms are often used as the underlying technology that supports the secure boot of a system.

The OEM or the entity responsible for the initial firmware running on the chip creates a public/private key pair. This operation takes place in a secure facility, and the private key is safely stored with controlled access. Often specialized hardware security modules (HSMs) are used to generate, store and apply this key (i.e., the key never leaves the HSM and only authorized users use it).

The public part of that key becomes part of the device's RoT. This is the first trusted component that is used to verify any further software. Care must be taken to guarantee the correct public key is placed in the devices; this step is usually implemented on the manufacturing line during a process called "trust provisioning" (see "OEM closed state" section in Chapter 6).

The private key is used to sign the firmware that will be executed on the secure system. This is a sensitive process, and the ability to sign the binary needs to be correctly controlled by the OEM. If, for example, mistakes are made and binaries that are not ready for production are signed, these binaries can later be used to compromise deployed edge devices.

Consider many of the heterogeneous i.MX applications processors. They use a mechanism similar to the secure boot process called High Assurance Boot (HAB), which is shown in Figure 3.10.

Figure 3.10. High Assurance Boot

#### **SECURITY AND ISOLATION**

Cryptographic algorithms and protocols have been around for decades. They are trusted to be robust and reliable if used correctly. However, as shown by several cyberattacks, logical errors (also known as bugs) have proven to be easy-to-exploit weak links in securing edge computing systems. A bug that can be used to compromise the security of a system is known as a vulnerability. The larger the code base, the higher the number of vulnerabilities the software running on the system has. Android and Linux are good examples of this reality (see also Table 3.2.)

A mitigation technique used in systems that require a certain level of security is isolating the storage and processing of sensitive information to dedicated hardware. For example, secure elements have been used to protect keys and sensitive data in the smart card industry. This is also true for the PC industry, which uses Trusted Platform Module (TPM) technology to guarantee the integrity of the software running. This has proven to be an effective method that still provides some of the best protection available today. However, for several use cases, this solution has not scaled well because the need for processing power for sensitive operations has increased over the years. Hardware extensions were integrated in the SoC's CPU to add isolation capabilities to the system while taking full advantage of the performance advances of the CPU. Those isolation techniques were first introduced in PC, server and mobile devices, but they are now equally applicable to the SoCs used in edge devices.

Modern SoCs implement one or more of the following isolation techniques:

#### **Temporal isolation**

The core of the processor can be in different execution modes; the execution mode determines the amount of access the core has to the SoC resources (see "Trusted Execution Environment" section later in the chapter).

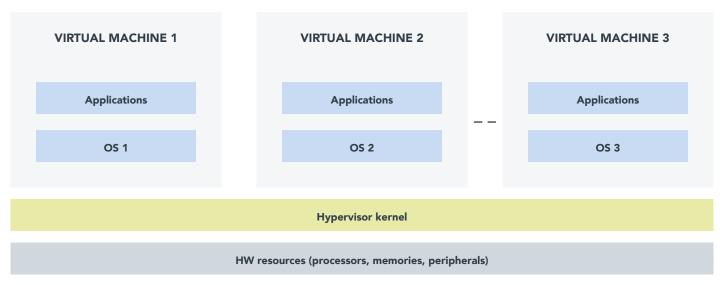

#### Virtualization

The resources of the SoC are split, and a hypervisor controls access to them (see "Virtualization" section later in the chapter). The hypervisor provides access to several OSs and applications that are all being executed in isolation.

#### **Multicore** isolation

In SoCs with more than one core, the tasks can be split over the various cores and different security policies can be applied per core.

#### **Secure enclaves**

These are additional cores in the SoC that are secure/hardened and that have their own private resources not accessible to the rest of the SoC.

#### Discrete components attached to the SoC

These are additional hardware components that can be attached to the SoC. They include secure elements, memory protection units, secure memory management units and discrete hardware firewalls around the SoC.

The next section explores one of these isolation techniques: the trusted execution environment.

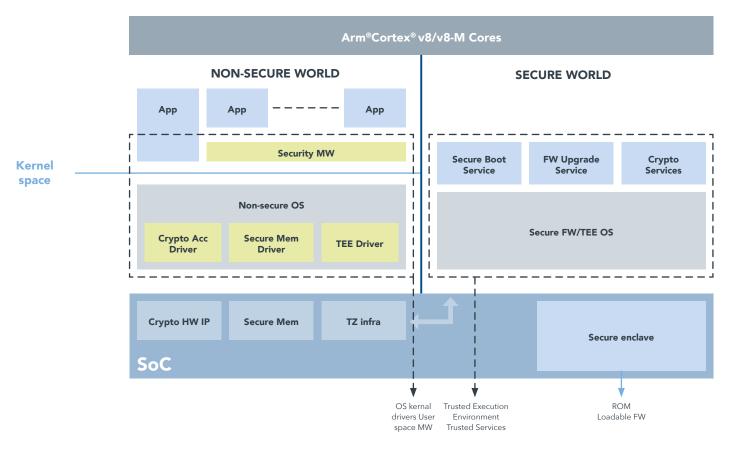

#### TRUSTED EXECUTION ENVIRONMENT

The first category of hardware extension is designed to isolate trusted functions. The concept of a Trusted Execution Environment (TEE) was introduced in the early 2000s to address these new requirements. The TEE implements a safe zone within the application processor. Large OSs such as Linux and Android potentially expose numerous vulnerabilities, so they are considered untrusted and execute outside the TEE in a zone known as the Rich Execution Environment (REE). Software that is carefully written with security in mind and is easily auditable runs inside the TEE. To satisfy those needs, CPU architecture extensions, including hardware support for this partitioning of trusted and untrusted software, have emerged from several hardware vendors. Some of these extensions include Intel SGX?, AMD Secure Encryption Virtualization (SEV)<sup>10</sup> and Arm® TrustZone®<sup>11</sup>. Several software implementations are available, including proprietary and open-source options. Most of these implementations follow a similar software architecture for which the software running in the TEE offers a collection of services to the software running in the REE. The TEE stack itself is usually made of the following two components:

- The TEE core component, also known as the TEE kernel, offers the core isolation mechanism

as well as basic services like cryptographic and storage services.

- TEE applications, running on top of the TEE core components, offer customization and user programmability for dedicated services to the REE.

On edge computing devices, several trusted service applications run in the TEE including the following:

**Local HSM** (for example, to serve as a local certification authority as mentioned in PKI)

Content protection and digital rights management (DRM)

**Secure boot**

Machine learning protection

Firmware update

TEEs are used to partition not only the processor and the memories but also the peripherals. Some TEE technologies enable a separation of the devices so that some devices are accessible only by the TEE and not by the REE.

$<sup>{}^{10}</sup> Reference: https://www.amd.com/en/processors/amd-secure-encrypted-virtualization$

#### SOFTWARE STACK EXAMPLE

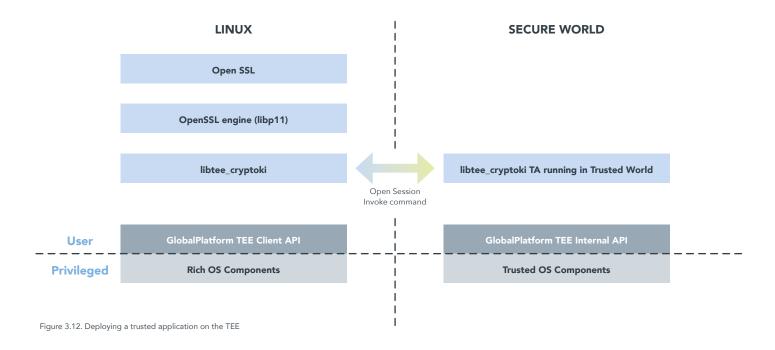

Figure 3.11. Edge device software stack with nonsecure world in Linux and secure world in OP-TEE

OpenSSL is an open-source software library that provides TLS protocols implementation and cryptographic operation functions. It is widely used by applications running Linux OS on edge devices for securing communication channels. One OpenSSL example shows how an edge device software stack can be deployed to secure key assets material while keeping, from an application point of view, the same interface.

Figure 3.11 shows an edge device software stack. It relies on Arm TrustZone isolation to provide two software execution environments. The nonsecure world execution environment is running the rich Linux OS. The secure world execution is running open, portable OP-TEE<sup>12</sup>. It is an open-source implementation of TEE that complies with the Global Platform TEE specification. It works through API core functionalities such as cryptographic, key and storage operations. Those functions also can be accelerated in hardware. This is the case for cryptographic operations that are accelerated using the CAAM hardware on i.MX devices. Trusted applications use those APIs to offer services to the Linux OS. In the OpenSSL example, this trusted application offers cryptographic operation with keys that are protected by the TEE and saved in secure storage.

A standard interface is used to prevent the OpenSSL from being modified. PKCS11 is one of the PKC standards. It is a platform-independent API for accessing tokens like HSMs or smart cards. Most of the Linux applications that use PKC have an option to use the PKCS11 interface. This is the case for most web browsers, including Firefox and Chrome, and for OpenSSL.

Figure 3.12 shows the final architecture for the OpenSSL example. A trusted application is deployed on the TEE and exposes PKC functions to a library running on Linux OS. This library exposes a PKCS11 API that is then used by OpenSSL to offer cryptographic functions to the entire application running on the rich OS.

The keys of the edge-connected device are safely stored in the TEE, while a Linux application, such as a trust provisioning or firmware update, can use them to establish a safe TLS connection with a remote server.

#### **VIRTUALIZATION**

Another isolation technique is virtualization (with or without support of the hardware). The applications performed by the edge device are clustered in virtual machines that are executed by a hypervisor that manages the sharing of the SoC hardware resources among the different virtual machines (see Figure 3.13). Malware infesting one of the virtual machines (e.g., a virtual machine installing an application from an unreliable source on the internet) cannot alter the behavior of the other virtual machines. It also cannot access the sensitive information managed by the other virtual machines as long as the attacker does not succeed in attacking the hypervisor as well. There are several ways to virtualize, for example, using a XEN hypervisor or a "docker" implementation. This approach is more secure because a hypervisor is a specific software implementation of a minimal OS. It has a smaller attack surface, and it can be audited for security when compared with Linux or Android complex systems. Table 3.2 illustrates this difference by listing the number of Common Vulnerabilities and Exposures (CVE) referring to XEN, Linux and Android. Note: Just because the OS is mentioned in a Table 3.2 entry doesn't mean it is per se an issue, but inclusion in this table shows the relative numbers for a hypervisor compared with those of large, complex OSs. In addition, modern cores used in SoCs provide some hardware support for this virtualization. The most common one is a memory manager that ensures the secure partionning of the memory.

Figure 3.13. Virtualization

| Year | Total number of entries in CVE database | Total number of entries mentioning XEN | Total number of entries mentioning Linux | Total number of entries mentioning Android |

|------|-----------------------------------------|----------------------------------------|------------------------------------------|--------------------------------------------|

| 2018 | 21837                                   | 95                                     | 650                                      | 725                                        |

| 2019 | 21431                                   | 90                                     | 710                                      | 1445                                       |

| 2020 | 30890                                   | 100                                    | 405                                      | 1241                                       |

Table 3.2. Number of CVE entries per OS13

<sup>13</sup>Reference: https://cve.mitre.org/

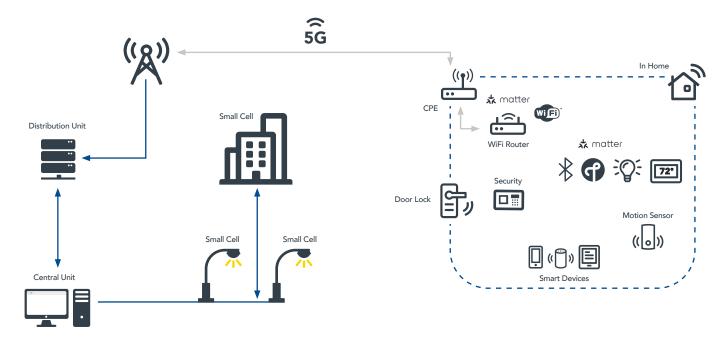

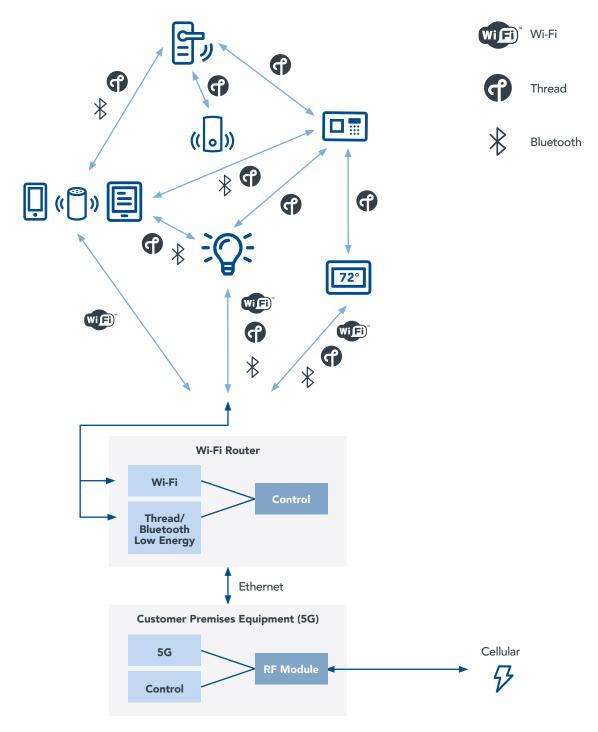

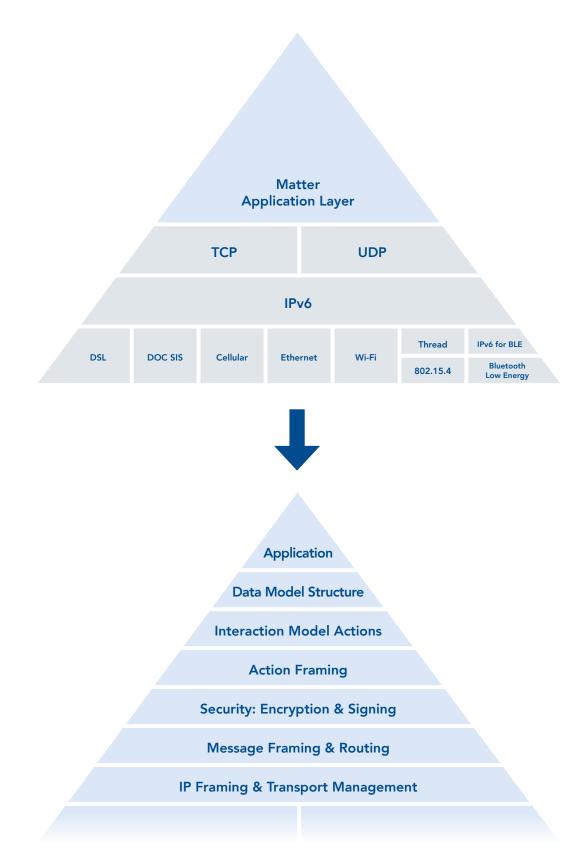

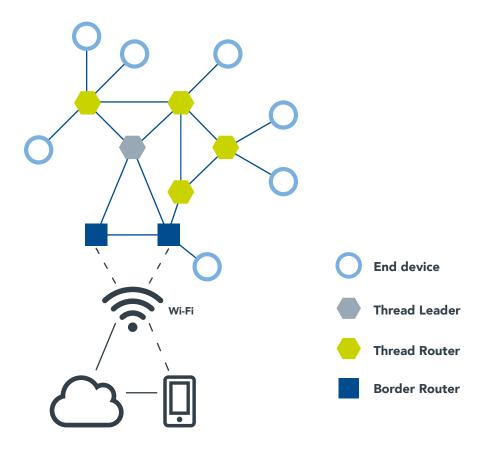

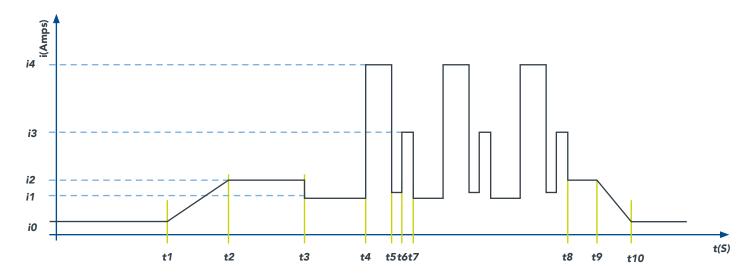

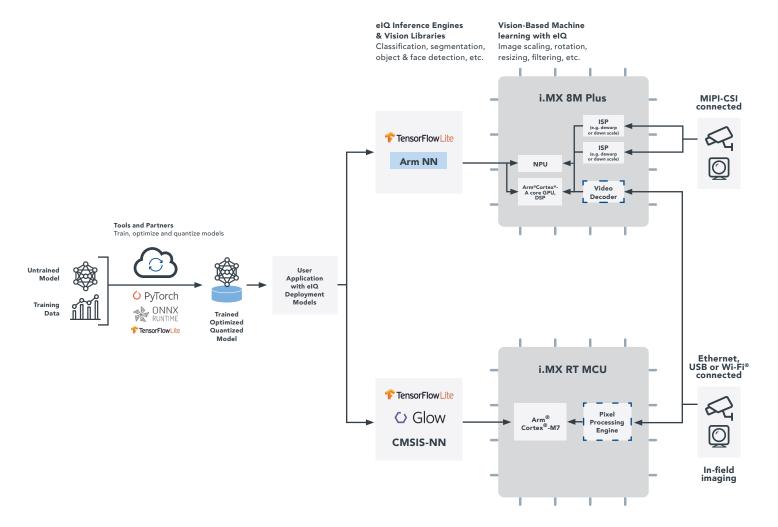

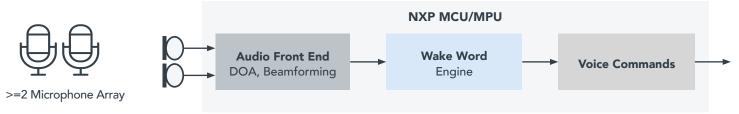

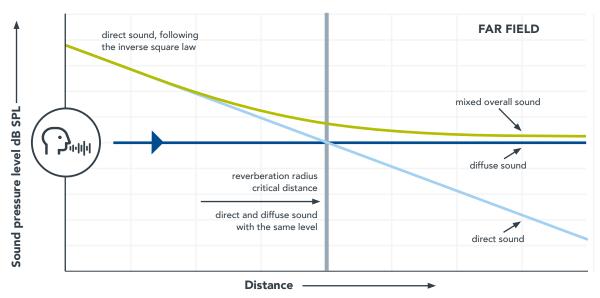

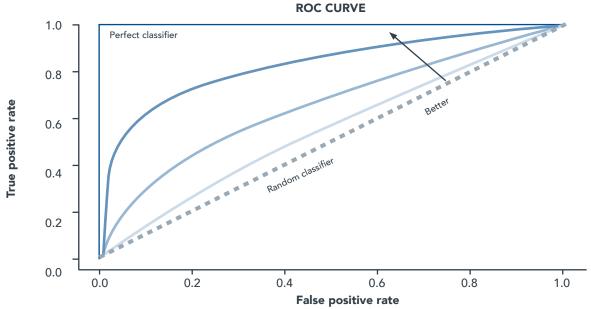

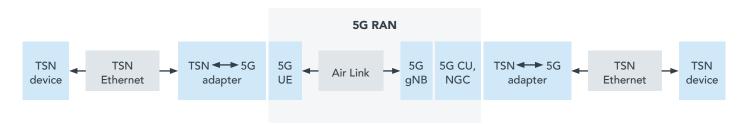

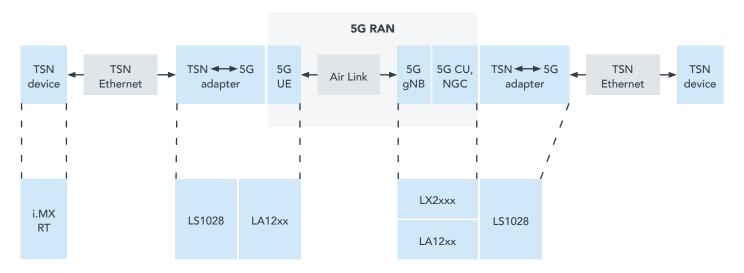

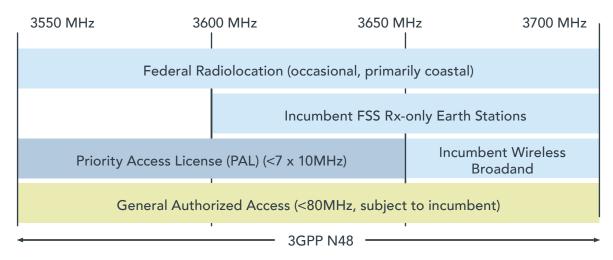

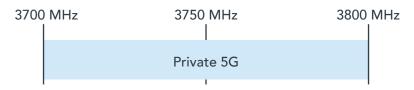

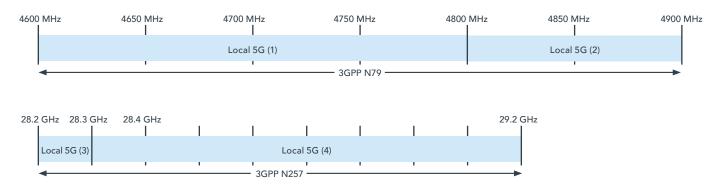

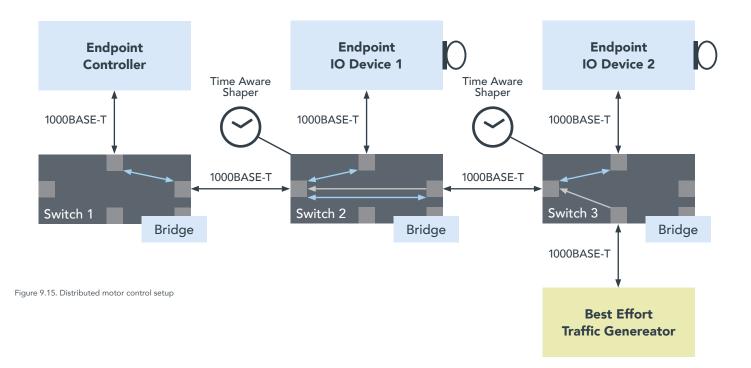

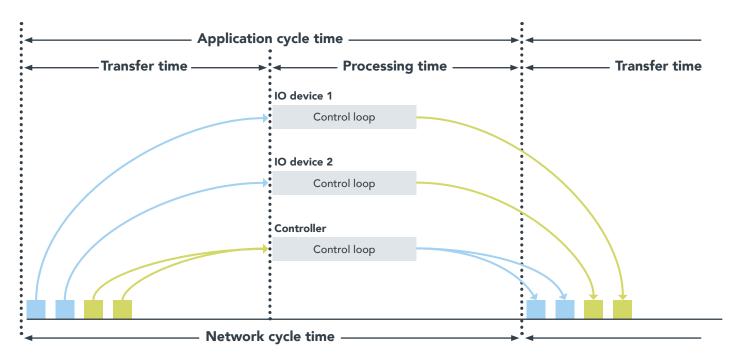

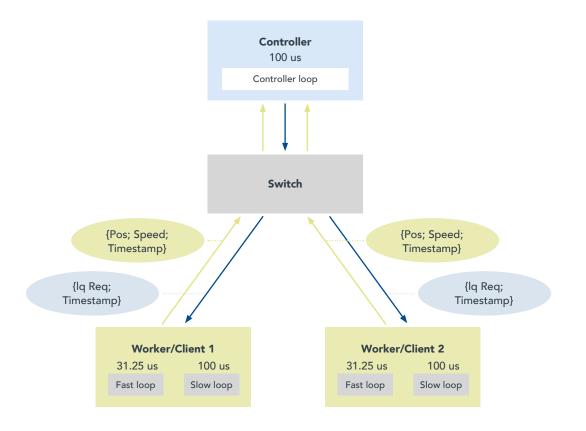

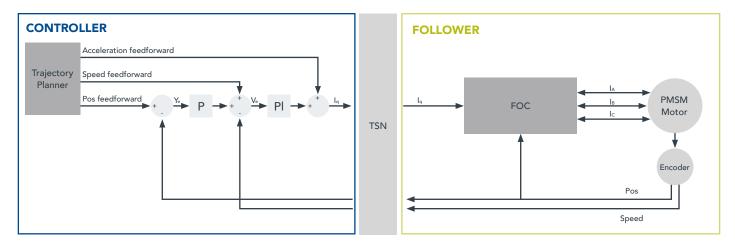

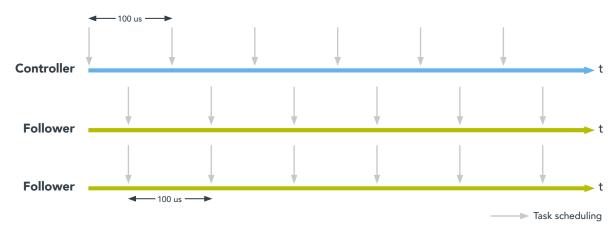

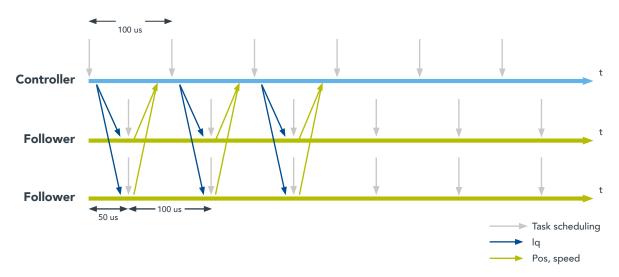

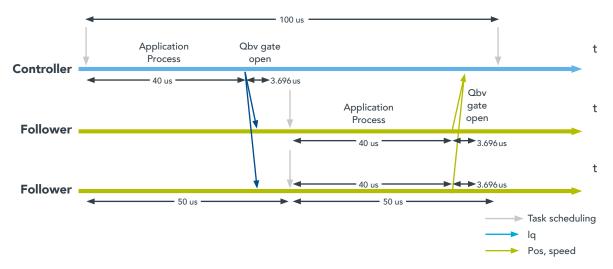

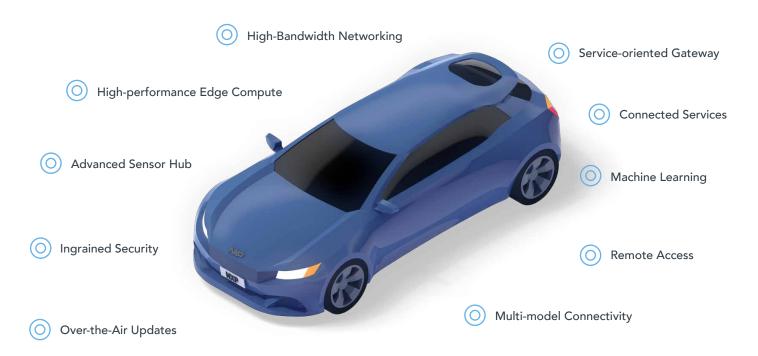

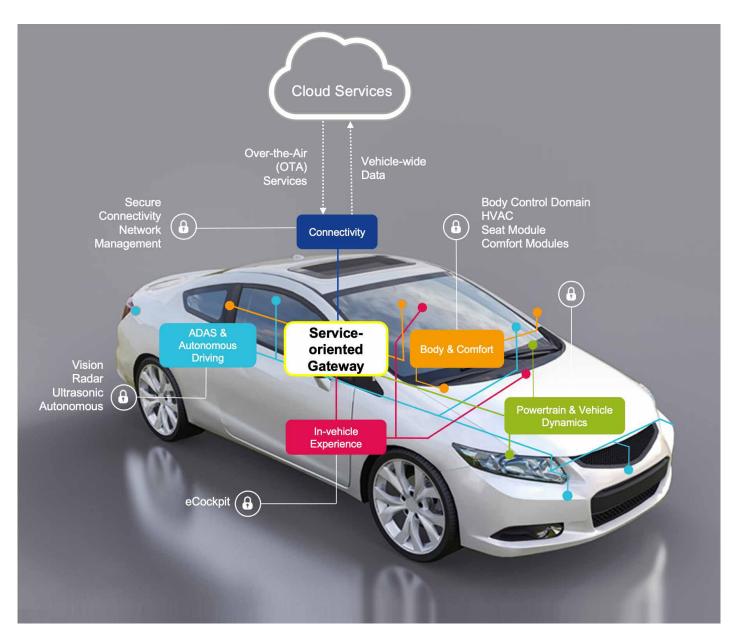

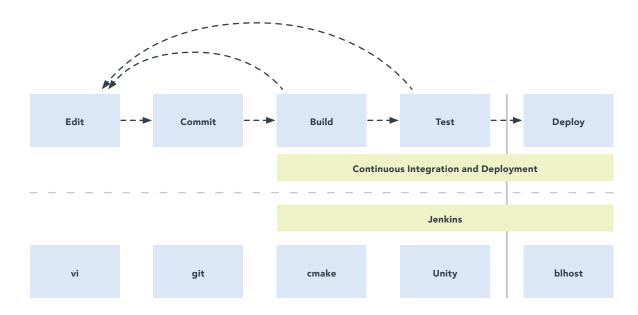

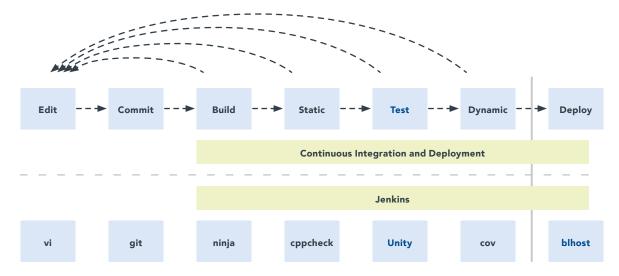

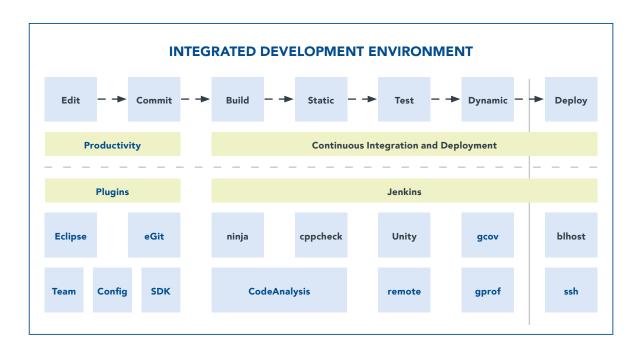

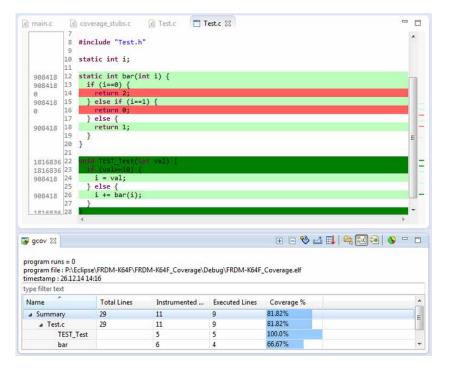

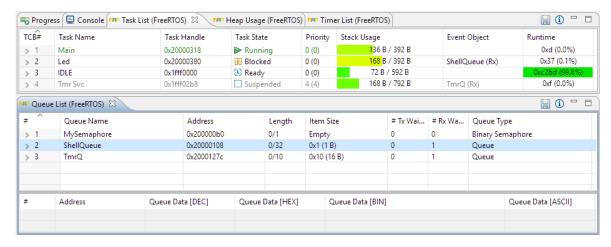

#### **SECURITY CERTIFICATIONS**